Wishbone (computer bus)

| Created by | Silicore Corporation |

|---|---|

| Width in bits | 8, 16, 32, 64 |

| Style | Parallel |

| Hotplugging interface | No (On chip bus) |

| External interface | No |

The Wishbone Bus is an open source hardware computer bus intended to let the parts of an integrated circuit communicate with each other. The aim is to allow the connection of differing cores to each other inside of a chip. The Wishbone Bus is used by many designs in the OpenCores project.

Wishbone is intended as a "logic bus". It does not specify electrical information or the bus topology. Instead, the specification is written in terms of "signals", clock cycles, and high and low levels.

This ambiguity is intentional. Wishbone is made to let designers combine several designs written in Verilog, VHDL or some other logic-description language for electronic design automation (EDA). Wishbone provides a standard way for designers to combine these hardware logic designs (called "cores"). Wishbone is defined to have 8, 16, 32, and 64-bit buses. All signals are synchronous to a single clock but some slave responses must be generated combinatorially for maximum performance. Wishbone permits addition of a "tag bus" to describe the data. But reset, simple addressed reads and writes, movement of blocks of data, and indivisible bus cycles all work without tags.

Wishbone is open source. To prevent preemption of its technologies by aggressive patenting, the Wishbone specification includes examples of prior art, to prove its concepts are in the public domain.

A device does not conform to the Wishbone specification unless it includes a data sheet that describes what it does, bus width, utilization, etc. Promoting reuse of a design requires the data sheet. Making a design reusable in turn makes it easier to share with others.

The Simple Bus Architecture is a simplified version of the Wishbone specification.[1]

Wishbone topologies

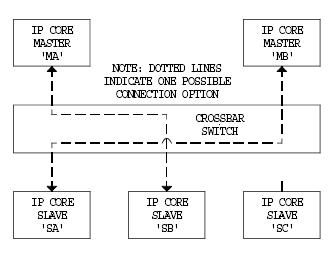

[edit]Wishbone adapts well to common topologies such as point-to-point, many-to-many (i.e. the classic bus system), hierarchical, or even switched fabrics such as crossbar switches. In the more exotic topologies, Wishbone requires a bus controller or arbiter, but devices still maintain the same interface.

Shared bus

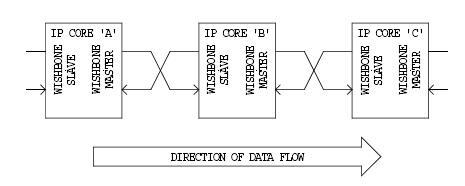

[edit]Data flow

[edit]Crossbar switch

[edit]Comparisons

[edit]Wishbone control signals compared to other system on a chip (SoC) bus standards:

| Wishbone | Avalon Bus | Description |

|---|---|---|

| cyc | = !write_n or !read_n | indicates that a valid bus cycle is in progress |

| stb | = chipselect | indicates a valid data transfer cycle |

| we | = !write_n and read_n | indicates whether the current local bus cycle is a READ or WRITE cycle. The signal is negated during READ cycles, and is asserted during WRITE cycles. |

| ack | = !waitrequest | indicates the termination of a normal bus cycle by slave device. |

| Avalon Bus | Wishbone | Description |

|---|---|---|

| chipselect | = stb | indicates that slave device is selected. |

| write_n | = !(cyc and we) | indicated that master requests to write to slave device. |

| read_n | = !(cyc and !we) | indicated that master requests to read from slave device. |

| waitrequest | = !ack | indicates that slave requests that master wait. |

See also

[edit]References

[edit]External links

[edit]- Wishbone Version B3- The PDF specification

- Wishbone Version B4- PDF specification of latest version of Wishbone

- appnote_01- Combining WISHBONE interface signals application note

- Comparison to other SoC buses

- Wishbone@OpenCores

- Wishbone@FPGA-Cores.com