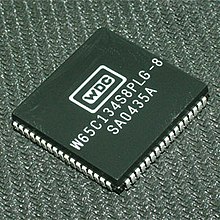

WDC 65C134

The Western Design Center (WDC) W65C134S is an 8-bit CMOS microcontroller based on a W65C02S processor core, which is a superset of the MOS Technology 6502 processor.

The W65C134S consists of a fully static 8-bit W65C02S CPU core, 4 KB of ROM containing a machine language monitor, 192 bytes of SRAM, two 16 bit timers, one 16-bit Watch-Dog Timer (WDT) with "restart" interrupt, one UART with baud rate timer, a low power Serial Interface Bus (SIB) configured as a token passing local area network, twenty-two priority encoded interrupts, two crystal inputs (slow 32.768KHz and fast up to 8-MHz), Bus Control Register (BCR) for external memory bus control, interface circuitry for peripheral devices, and many low power features. The W65C134S has been developed for high-reliability applications, as well as where minimum power is required.

Features

[edit]- CMOS low power process

- Operating ambient temperature range of -40 °C to +85 °C

- Single 2.8V to 5.5V power supply

- Static to 8 MHz clock operation, as well as 32.768KHz capability

- W65C02S compatible CPU

- 8-bit parallel processing

- Variable length stack

- True indexing capability

- Fifteen addressing modes

- Decimal or binary arithmetic

- Pipeline architecture

- Fully static CPU

- Single chip microcomputer

- Many power saving features

- 56 CMOS compatible I/O lines

- 4096 x 8 ROM on chip

- 192 x 8 RAM on chip

- Low power modes

- WAIt for interrupt

- SToP the clock

- Fast oscillator start and stop feature

- Twenty-two priority encoded interrupts

- BRK software interrupt

- RESET "RESTART" interrupt

- NMIB Non-Maskable Interrupt input

- SIB Interrupt

- IRQ1B level interrupt input

- IRQ2B level interrupt input

- 2 timer edge interrupts

- 7 positive edge interrupt inputs

- 5 negative edge interrupt inputs

- Asynchronous Receiver Interrupt

- Asynchronous Transmitter Interrupt

- UART 7/8-bit w/wo odd or even parity

- 16M byte segmented address space

- 64K byte linear address space

- 4 x 16 bit timer/counter

- Bus control register for external memory

- Internal or external ROM

- 8 Decoded Chip Select outputs

- Surface mount 68 and 80 lead packages

- Real time clock features

- Time of Day (ToD) clock features

See also

[edit]- WDC 65C265 - a 16-bit microcontroller based around a WDC 65C816 processor core

References

[edit]Further reading

[edit]External links

[edit]- W65C134S webpage - Western Design Center (WDC)

- W65C134S datasheet - WDC

- W65C134S monitor ROM manual - WDC