User:Ralf Moses/sandbox

The CRUVI FPGA Card is a daughter card standard specifically tailored to the needs of FPGAs.

Background

[edit]The expansion bus interface is designed to create an open ecosystem of function modules for high-performance peripheral connectivity. Its main focus is on supporting FPGA and FPGA SoC devices from all major manufacturers like Altera, Lattice, Microchip and Xilinx.

The word "CRUVI" is a combination of the Estonian word "KRUVI" for screw and the letter "C", which refers to the half of the hexagonal screw head. In this case, the "K" was replaced with "C" to emphasize the reference to the screw head.

Overview

[edit]It can be used to build high performance prototypes, for system integration and testing to build complex systems from smaller building blocks to iterate quickly and reduce cost. Create custom test systems for production functional testing. It´s a perfect platform for your next high-performance semiconductor evaluation boards and systems.

The carrier module supplies the power supply, the input/output voltage and controls the functions of the peripheral modules.

The CRUVI open standard coexists between low speed, low pin-count like Pmod Interface devices and high-performance, high pin-count (HPC), 400 I/O FPGA Mezzanine Card (FMC) peripherals.

Three board-to-board connectors are specified: CRUVI-LS (Low Speed), CRUVI-HS (High Speed) and CRUVI-GT (Gigabit Transceiver) PCIe Gen 5.0 capable.

Bridging adapter exists to convert signals from Pmod to CRUVI-LS (CR00025), from FMC to CRUVI-HS (CR00101, CR00111) and FMC to CRUVI-GT (CR00112).

History of CRUVI specification

[edit]International contributors to define the open source CRUVI specification are Trenz Electronic GmbH, Arrow Electronics, Samtec, Flinders University, Synaptic Laboratories Ltd, Symbiotic EDA and MicroFPGA UG.

| Year | Version | Notes | Refs |

|---|---|---|---|

| 2021 | 1.0.7 -alpha | first release | |

| 2024 | 2.0.1 -alpha | neu: CRUVI-GT (Gigabit Transceiver) | [1] |

Structure and description of the carrier modules

[edit]Single, double or triple width modules are allowed and they have more mounting holes.

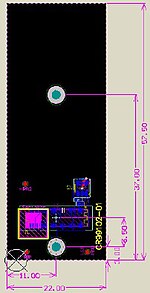

A triple size of space on carrier board is 67.72 x 57.5 mm² (2.66535 x 2.26378 inch²). There are 3 slots. The mounting holes (1 to 6) for M2 screws are 2.2 mm (0.0866 inch) diameter and need SMD spacer for mechanically fixing. The CR99201 PCB template has LS and HS connectors named: AX, BY and CZ. The CR99500[2] PCB template has LS, HS and GT connectors.

- triple maximum size carrier board

It is recommended for all FPGA host boards with CRUVI slots provide LiteX platform support files.[3]

Structure and description of the peripheral modules

[edit]There are different single peripheral module possible, flexible and scalable by size LS, HS and GT connectors. Mounting holes are for M2 screws 2.2 mm (0.0866 inch) diameter.

CRUVI connector specification

[edit]peripheral board specification

[edit]There are different single peripheral module possible, flexible and scalable by size LS, HS and GT connectors. Mounting holes are for M2 screws 2.2 mm (0.0866 inch) diameter.

It is recommended to have EEPROM with I2C for identification of peripheral module with a specific address number.

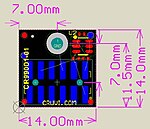

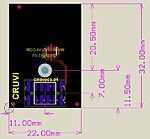

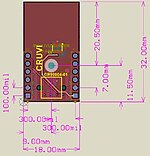

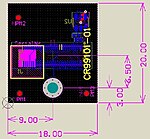

| L x H [mm²] / [inch²] | speed | PCB template [4] | Note |

|---|---|---|---|

| 14 x 14 / 0.55 x 0.55 | LS | CR99001 |

identification EEPROM is included; This template is usefull for I2C, I3C, SPI sensor, I2S PDM MEMS microphones, programmable oscillator, ADC, DAC or SPI (QSPI) Flash memory device in BGA24 or SO-8 package. |

| 14 x 14 / 0.55 x 0.55 | LS | CR99002 | same as CR99001 with added u.Fl connectors for I/O |

| 22 x 32 / 0.87 x 1.2598 | LS | CR99003 |

maximum size one-wide half-length, identification EEPROM is included |

| 18 x 32 / 0.71 x 1.26 | LS | CR99004 |

This template is usefull to convert into Pmod compatible connector (CR00005). |

| 22 x 30 / 0.87 x 1.18 | LS | CR99005 |

is half-length LS module with two SMA connectors |

| 18 x 20 / 0.71 x 0.79 | HS | CR99101 |

minimal size HS Module; good for HyperRAM or HyperFlash (CR00041), eMMC (CR00049) or loopback adapter for CRUVI-HS (CR00091) |

| 22 x 57.5 / 0.87 x 2.26 | HS | CR99102 |

maximum sized single-width HS module; good for signal test adapter to probed with scope or logic analyzer (CR00026), for high speed interfaces like USB-C, HDMI (CR00240), MIPI CSI/DSI, SDIO, xGMII Ethernet (CR0020x) and LVDS ADC (1 to 4 data lane) |

| GT | CR99103 |

comming soon, good for HDMI output (CR00240), JESD204B ADC (CR00401), loopback adapter for CRUVI-GT (CR00092) |

LS Low Speed, HS High Speed and GT Gigabit Transceiver connector

[edit]| Connector | LS Low Speed | HS High Speed | GT Gigabit Transceiver |

|---|---|---|---|

| Carrier side connector | CLT-106-02-F-D-A-K | SS4-30-3.50-L-D-K | ADF6-20-03.5-L-4-2 |

| Peripheral side connector | TMMH-106-04-F-DV-A-M | ST4-30-1.50-L-D-P | ADM6-20-01.5-L-4-2 |

| Pin no | 12 (6 per row) | 60 (30 per row) | 80 (20 per row) |

| pitch [mm] / [inch] | 2 / 0.787 | 0.4 / 0.016 | 0.635 / 0.025 |

| stacked height [mm] / [inch] | 4.78 to 5.29 /0.188 to 0.208 | 5 / 0.197 | |

| speed rating [GHz] / [Gbps] | 5.5 / 11 | 13.5 / 27 (single ended)

15.5 / 31 (differential) |

32 |

| Single ended I/O pins (VCCIO) | 8 | 37 (28 adj.) + (9 fixed 3.3V) | 8 + I2C |

| max. differential I/O | no | max. 12 LVDS | max. 4 lanes + REFCLK |

| Power Supply | adj., 3.3V, 5V | ||

| Current rating per pin [A] | 4.1 (2-pin powered) | 1.6 (2-pin powered) | 1.34 (4-pin powered) |

| max. Temperatur range [°C] | -55 to 125 | ||

CRUVI-LS pinout and signal description

[edit]| Pin | Primary | Signal | Pin | Primary | Signal |

|---|---|---|---|---|---|

| 1 | SDA | I2C(SDA), SMBUS(SDA) | 7 | D1 | UART(RXD1), SD(D1), SPI(MISO), QSPI(D1), JTAG(TDI) |

| 2 | SCL | I2C(SCL), SMBUS(SCL) | 8 | CLK | UART(RTS), SD(CLK), SPI(CLK), QSPI(CLK), JTAG(TCK) |

| 3 | D3 | UART(RST), SD(TXD0), QSPI(D3), JTAG(nRST) | 9 | D0 | UART(TXD1), SD(D0), SPI(MOSI), QSPI(D0) JTAG(TDO) |

| 4 | SEL | UART(CTS), SD(CMD), SPI(SEL), QSPI(SEL), JTAG(TMS) | 10 | VCC | Power 3.3V |

| 5 | D2 | SMBUS(INT), UART(RXD0), SD(D2), QSPI(D2), JTAG(RFU) | 11 | RFU | tbd |

| 6 | GND | Ground | 12 | VBUS | Power 5V |

CRUVI-HS pinout and signal description

[edit]| Pin | Primary Function | Note | Pin | Primary Function | Note | Pin | Primary Function | Note | Pin | Primary Function | Note |

|---|---|---|---|---|---|---|---|---|---|---|---|

| 1 | RFU1 | 16 | A0_N | Transceiver I/O | 31 | GND | Ground | 46 | A5_N | Transceiver I/O | |

| 2 | HSIO | 17 | B0_N | Transceiver I/O | 32 | A3_P | 47 | B5_N | Transceiver I/O | ||

| 3 | ALERT/IRQ | 18 | GND | Ground | 33 | B3_P | Transceiver I/O | 48 | GND | Ground | |

| 4 | VCC | 3,3V | 19 | GND | Ground | 34 | A3_N | 49 | GND | Ground | |

| 5 | SDA | 20 | A1_P | Transceiver I/O | 35 | B3_N | Transceiver I/O | 50 | RFU2_P | ||

| 6 | HSO | 21 | B1_P | Transceiver I/O | 36 | VADJ | 1.2 to 3.3V | 51 | DI/TDI | JTAG, SPI(MISO) | |

| 7 | SCL | 22 | A1_N | Transceiver I/O | 37 | GND | Ground | 52 | RFU2_N | ||

| 8 | HSRST | 23 | B1_N | Transceiver I/O | 38 | A4_P | Transceiver I/O | 53 | DO/TDO | JTAG, SPI(MOSI) | |

| 9 | VCC | 3.3V | 24 | GND | Ground | 39 | B4_P | Transceiver I/O | 54 | GND | Ground |

| 10 | HSI | 25 | GND | Ground | 40 | A4_N | Transceiver I/O | 55 | SEL/TMS | JTAG, SPI(SEL) | |

| 11 | REFCLK | 26 | A2_P | 41 | B4_N | Transceiver I/O | 56 | RFU_P | |||

| 12 | GND | Ground | 27 | B2_P | Transceiver I/O | 42 | GND | Ground | 57 | MODE | JTAG EN |

| 13 | GND | Ground | 28 | A2_N | 43 | GND | Ground | 58 | RFU_N | ||

| 14 | A0_P | Transceiver I/O | 29 | B2_N | Transceiver I/O | 44 | A5_P | Transceiver I/O | 59 | SCK/TCK | JTAG, SPI(CLK) |

| 15 | B0_P | Transceiver I/O | 30 | GND | Ground | 45 | B5_P | Transceiver I/O | 60 | VBUS | 5V |

CRUVI-GT pinout and signal description

[edit]| Pin | Primary Function | Note | Pin | Primary Function | Note | Pin | Primary Function | Note | Pin | Primary Function | Note |

|---|---|---|---|---|---|---|---|---|---|---|---|

| 1 | 21 | 41 | 61 | ||||||||

| 2 | 22 | 42 | 62 | ||||||||

| 3 | 23 | 43 | 63 | ||||||||

| 4 | 24 | 44 | 64 | ||||||||

| 5 | 25 | 45 | 65 | ||||||||

| 6 | 26 | 46 | 66 | ||||||||

| 7 | 27 | 47 | 67 | ||||||||

| 8 | 28 | 48 | 68 | ||||||||

| 9 | 29 | 49 | 69 | ||||||||

| 10 | 30 | 50 | 70 | ||||||||

| 11 | 31 | 51 | 71 | ||||||||

| 12 | 32 | 52 | 72 | ||||||||

| 13 | 33 | 53 | 73 | ||||||||

| 14 | 34 | 54 | 74 | ||||||||

| 15 | 35 | 55 | 75 | ||||||||

| 16 | 36 | 56 | 76 | ||||||||

| 17 | 37 | 57 | 77 | ||||||||

| 18 | 38 | 58 | 78 | ||||||||

| 19 | 39 | 59 | 79 | ||||||||

| 20 | 40 | 60 | 80 |

References

[edit]- ^ "CRUVI specification v2.0.1 (2024)" (PDF). Retrieved 2024-05-17.

- ^ "PCB Vorlage CRUVI peripheral Module". Retrieved 2024-05-17.

- ^ "LiteX platform support files for FPGA host boards with CRUVI slots". Retrieved 2024-05-17.

- ^ "PCB template CRUVI peripheral boards". Retrieved 2023-12-19.

External links

[edit]- CRUVI Webpage

- Trenz Electronic develops and manufactures CRUVI + FPGA (SoC) modules for business and science

- Trenz Electronic and their partners created a new FPGA expansion bus called CRUVI published 2023-05-11

- Arrow reveals first Dev Board for Intel Agilex 5 FPGAs, with two more boards planned published 2023-11-27

- Software is integrated into VHDPlus IDE for CRUVI solutions

- Synaptic Laboratories Ltd (SLL) is contributor to the exciting open source CRUVI standard for memory controller and related technologies. i.e. HyperBus, OctaBus, Xccela Bus and JEDEC xSPI memory