Talk:Flynn's taxonomy

| This article is rated C-class on Wikipedia's content assessment scale. It is of interest to the following WikiProjects: | ||||||||||||||||||||||||

| ||||||||||||||||||||||||

| This article is based on material taken from the Free On-line Dictionary of Computing prior to 1 November 2008 and incorporated under the "relicensing" terms of the GFDL, version 1.3 or later. |

Probably all of the sub-pages (e.g. MIMD) should redirect to Flynn's taxonomy.--aciel 21:15, 5 February 2006 (UTC)

- hmmm that would make this one MASSIVE page, i'm not sure that's a good idea Lkcl (talk) 17:10, 17 June 2021 (UTC)

SPMD is not Single Process Multiple Instruction

[edit]This is with reference to SPMD discussion. In no way SPMD should mean Single Process Multiple Instruction. This is because if we use the term Process in place of Program, this would take us to somewhere which is totally different context.

Program is the blueprint of the process or we can say that Program in execution is called process. If we say SPMD to Single Process Multiple Instruction then we mean that all processors are executing the same Process then the question arises how?

The true case is the program, which is common to all the processors under consideration.—The preceding unsigned comment was added by 203.101.168.14 (talk • contribs) .

Images, please verify work

[edit]Would anyone care to verify my work here?

| SISD |

|

| SIMD |

|

| MISD |

|

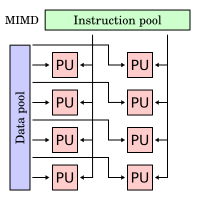

| MIMD |

|

Comments here or my talk page are welcome. Cburnett 02:29, 12 June 2007 (UTC)

- 12 days and no comment so I put them in the article. Cburnett 03:40, 25 June 2007 (UTC)

-

- i must apologise, it's 14 years since these were added and i have only just recently started critiquing this area of computer science. the images are great, i was going to do something similar, including Vector Processing. there is however some important information missing from the diagrams: SIMD takes individual *registers* and fragments (subdivides) them into what is termed "Lanes" inside the ALU. by saying "Data pool" this distinction, which is actually extremely important when it comes to classifying Vector Processors, is not possible to make. see Duncan's Taxonomy for details. Lkcl (talk) 23:32, 13 June 2021 (UTC)

Correct citation

[edit]Flynn, M.J.; , "Very high-speed computing systems," Proceedings of the IEEE , vol.54, no.12, pp. 1901- 1909, Dec. 1966 doi: 10.1109/PROC.1966.5273 URL: http://ieeexplore.ieee.org/stamp/stamp.jsp?tp=&arnumber=1447203&isnumber=31091 — Preceding unsigned comment added by 129.132.211.73 (talk) 22:44, 10 December 2011 (UTC)

Modification to definition of Single Instruction, Single Data Stream classification

[edit]An SISD architecture ***may*** implement instruction-level parallelism.

Use of a single instruction stream does not preclude segmentation of an instruction inside a uniprocessor along the stages of the pipeline. [1]

Similarly, use of a single instruction stream with a superscalar uniprocessor may result in two instructions simultaneously (i.e. in parallel execution) undergoing processing within different functional units of the superscalar uniprocessor. [2] Edepa (talk) 18:05, 28 December 2012 (UTC)

- what you are referring to is termed "multi-issue" execution. the crucial thing about multi-issue is that it must look exactly like single-instruction execution. the technical term for this is called "Preserving Program Order". it is not appropriate to change the taxonomy group of this page to account for this because the taxonomy itself effectively refers to Program Order. a sub-taxonomy might however be appropriate, or something which mentions multi-issue etc. etc. Lkcl (talk) 23:46, 13 June 2021 (UTC)

References

- ^ John L. Hennessy, David A. Patterson, Computer Architecture: A Quantitative approach, Fourth Edition, Appendix A

- ^ http://en.wikipedia.org/wiki/Superscalar

External links modified

[edit]Hello fellow Wikipedians,

I have just added archive links to 2 external links on Flynn's taxonomy. Please take a moment to review my edit. If necessary, add {{cbignore}} after the link to keep me from modifying it. Alternatively, you can add {{nobots|deny=InternetArchiveBot}} to keep me off the page altogether. I made the following changes:

- Added archive https://web.archive.org/20060901114042/http://www.cisl.ucar.edu/docs/lightning/program.jsp to http://www.cisl.ucar.edu/docs/lightning/program.jsp

- Added archive https://web.archive.org/20070203153908/http://www.cisl.ucar.edu:80/docs/ibm/ref/parallel.html to http://www.cisl.ucar.edu/docs/ibm/ref/parallel.html

When you have finished reviewing my changes, please set the checked parameter below to true to let others know.

This message was posted before February 2018. After February 2018, "External links modified" talk page sections are no longer generated or monitored by InternetArchiveBot. No special action is required regarding these talk page notices, other than regular verification using the archive tool instructions below. Editors have permission to delete these "External links modified" talk page sections if they want to de-clutter talk pages, but see the RfC before doing mass systematic removals. This message is updated dynamically through the template {{source check}} (last update: 5 June 2024).

- If you have discovered URLs which were erroneously considered dead by the bot, you can report them with this tool.

- If you found an error with any archives or the URLs themselves, you can fix them with this tool.

Cheers. —cyberbot IITalk to my owner:Online 10:42, 17 October 2015 (UTC)

External links modified

[edit]Hello fellow Wikipedians,

I have just added archive links to one external link on Flynn's taxonomy. Please take a moment to review my edit. If necessary, add {{cbignore}} after the link to keep me from modifying it. Alternatively, you can add {{nobots|deny=InternetArchiveBot}} to keep me off the page altogether. I made the following changes:

- Added archive https://web.archive.org/20060910222800/http://www.tc.cornell.edu/Services/Education/Topics/Parallel/Distributed/+9.2+Strategies.htm to http://www.tc.cornell.edu/Services/Education/Topics/Parallel/Distributed/+9.2+Strategies.htm

When you have finished reviewing my changes, please set the checked parameter below to true to let others know.

This message was posted before February 2018. After February 2018, "External links modified" talk page sections are no longer generated or monitored by InternetArchiveBot. No special action is required regarding these talk page notices, other than regular verification using the archive tool instructions below. Editors have permission to delete these "External links modified" talk page sections if they want to de-clutter talk pages, but see the RfC before doing mass systematic removals. This message is updated dynamically through the template {{source check}} (last update: 5 June 2024).

- If you have discovered URLs which were erroneously considered dead by the bot, you can report them with this tool.

- If you found an error with any archives or the URLs themselves, you can fix them with this tool.

Cheers.—cyberbot IITalk to my owner:Online 06:13, 5 January 2016 (UTC)

Map-reduce is a good example of MPMD in practice

[edit]Googling produce various resources online; don't know which are citation worthy.79.179.108.47 (talk) 10:16, 13 May 2017 (UTC)

Cell microprocessor is MPMD?

[edit]There's no citations under "Multiple-Program, Multiple-data." And MPMD is not mentioned, either in abbreviation or in full, in Cell (microprocessor). Is this accurate? 2001:48F8:7032:612:917D:61C8:C7A4:5FD5 (talk) 20:45, 5 July 2020 (UTC)

- the cell processor was a pain in the ass to program and just as awkward to categorise. the PPE was i heard somewhere a standard SISD [[IBM A2I] Power ISA v2.06 core, but the processing elements were DMA-based. i'm not sure they were even capable of Turing-complete execution, i'll have to check and get back on that with a followup Lkcl (talk) 00:01, 14 June 2021 (UTC)

- "Each SPE is a dual issue in order processor composed of a "Synergistic Processing Unit"" so yes, it seems it is capable of Turing-complete execution. although extremely odd i'd say yes it's MIMD, but due to the DMA access it's definitely not SMP (page says not even any caches on the SPEs), probably NUMA or heterogenous or something. Lkcl (talk) 00:06, 14 June 2021 (UTC)

SIMT equals multithreading is wrong (misleading)

[edit]saying that SIMT is multithreading and linking to the article is plain wrong. SIMT synchronously broadcasts an instruction to multiple fully-functioning cores with their own regfiles, own LOAD/STORE, their own ALUs.

SIMT does NOT have separate Program Counters. there is ONLY ONE program counter used by the ONE instruction decoder, that instruction being broadcast to multiple cores.

multithreading has SEPARATE program counters, separate instruction decoders, separate issue engines.

thus, claiming that SIMT === multithreading is very misleading.

just because NVIDIA mentioned "threads" in the online documentation doesn't mean that it's multithreading. Lkcl (talk) 23:55, 13 June 2021 (UTC)

- thanks to guy harris for the flynn 1972 reference. fixed. also could not help put in a factually correct dig at NVIDIA's marketing claims, because SOLOMON came out in the 1960s, some 60 years before NVIDIA's "novel" architecture. whoops :) Lkcl (talk) 17:07, 17 June 2021 (UTC)

Claim that Flynn's SIMD Taxonomy does not have SIMT is false

[edit]see SIMD talk page, figure 5 of Flynn's 1972 paper contains a diagram that is exactly SIMT: broadcast of instruction to units with their own memory and registers.

whatever NVIDIA claim is "novel" is false. particularly given that Aspex Linedancer is *exactly* a Type (1) SIMD aka SIMT.

the only difference is that NVidia and AMD SIMT implementations have a memory bus per unit rather thsn isolated selfcontained memory. even the Aspex ASP's per-ALU memory is not isolated, it could be globally written/read.

these pages are a mess. Lkcl (talk) 20:33, 15 June 2021 (UTC)

here is the reference that guy found for a later 1972 paper by Flynn.[1] Lkcl (talk) 20:38, 15 June 2021 (UTC)

whoops no the 2nd one is 1972.[2] Lkcl (talk) 20:40, 15 June 2021 (UTC)

i've started on the corrections to misinformation here, at Flynn's taxonomy, by adding in the 1977 paper and the 3 subcategories that he describes. this page is the root of the misinformation on SIMD. once corrected everything else will fall into place Lkcl (talk) 15:00, 16 June 2021 (UTC)

starting to get this sorted. also editing the category which is hard to get to https://en.wikipedia.org/wiki/Template:Flynn%27s_taxonomy Lkcl (talk) 17:08, 17 June 2021 (UTC)

References

- ^ Flynn, Michael J. (December 1966). "Very high-speed computing systems" (PDF). Proceedings of the IEEE. 54 (12): 1901–1909. doi:10.1109/PROC.1966.5273.

- ^ Flynn, Michael J. (September 1972). "Some Computer Organizations and Their Effectiveness" (PDF). IEEE Transactions on Computers. C-21 (9): 948–960. doi:10.1109/TC.1972.5009071.