Zen (first generation)

The logo for the Zen microarchitecture is a closed ensō | |

| General information | |

|---|---|

| Launched | March 2, 2017[1] |

| Designed by | AMD |

| Common manufacturer | |

| CPUID code | Family 17h |

| Cache | |

| L1 cache | 64 KB instruction, 32 KB data per core |

| L2 cache | 512 KB per core |

| L3 cache | 8 MB per CCX (APU: 4 MB) |

| Architecture and classification | |

| Technology node | 14 nm (FinFET)[2] |

| Instruction set | AMD64 (x86-64) |

| Physical specifications | |

| Transistors |

|

| Cores | |

| Sockets | |

| Products, models, variants | |

| Product code names |

|

| Brand names | |

| History | |

| Predecessor | Excavator (4th gen) |

| Successor | Zen+ |

| Support status | |

| Supported | |

Zen is the first iteration in the Zen family of computer processor microarchitectures from AMD. It was first used with their Ryzen series of CPUs in February 2017.[4] The first Zen-based preview system was demonstrated at E3 2016, and first substantially detailed at an event hosted a block away from the Intel Developer Forum 2016. The first Zen-based CPUs, codenamed "Summit Ridge", reached the market in early March 2017, Zen-derived Epyc server processors launched in June 2017[11] and Zen-based APUs arrived in November 2017.[12]

Zen is a clean sheet design that differs from AMD's previous long-standing Bulldozer architecture. Zen-based processors use a 14 nm FinFET process, are reportedly more energy efficient, and can execute significantly more instructions per cycle. SMT has been introduced, allowing each core to run two threads. The cache system has also been redesigned, making the L1 cache write-back. Zen processors use three different sockets: desktop Ryzen chips use the AM4 socket, bringing DDR4 support; the high-end desktop Zen-based Threadripper chips support quad-channel DDR4 memory and offer 64 PCIe 3.0 lanes (vs 24 lanes), using the TR4 socket;[13][14] and Epyc server processors offer 128 PCIe 3.0 lanes and octa-channel DDR4 using the SP3 socket.

Zen is based on a SoC design.[15] The memory controller and the PCIe, SATA, and USB controllers are incorporated into the same chip(s) as the processor cores. This has advantages in bandwidth and power, at the expense of chip complexity and die area.[16] This SoC design allows the Zen microarchitecture to scale from laptops and small-form factor mini PCs to high-end desktops and servers.

By 2020, 260 million Zen cores have already been shipped by AMD.[17]

Design

[edit]

According to AMD, the main focus of Zen is on increasing per-core performance.[21][22][23]

New or improved features include:[24]

- The L1 cache has been changed from write-through to write-back, allowing for lower latency and higher bandwidth.

- SMT (simultaneous multithreading) architecture allows for two threads per core, a departure from the CMT (clustered multi-thread) design used in the previous Bulldozer architecture. This is a feature previously offered in some IBM, Intel and Oracle processors.[25]

- A fundamental building block for all Zen-based CPUs is the Core Complex (CCX) consisting of four cores and their associated caches. Processors with more than four cores consist of multiple CCXs connected by Infinity Fabric.[26] Processors with non-multiple-of-four core counts have some cores disabled.

- Four ALUs, two AGUs/load–store units, and two floating-point units per core.[27]

- Newly introduced "large" micro-operation cache.[28]

- Each SMT core can dispatch up to six micro-ops per cycle (a combination of 6 integer micro-ops and 4 floating point micro-ops per cycle).[29][30]

- Close to 2× faster L1 and L2 bandwidth, with total L3 cache bandwidth up 5×.

- Clock gating.

- Larger retire, load, and store queues.

- Improved branch prediction using a hashed perceptron system with Indirect Target Array similar to the Bobcat microarchitecture,[31] something that has been compared to a neural network by AMD engineer Mike Clark.[32]

- The branch predictor is decoupled from the fetch stage.

- A dedicated stack engine for modifying the stack pointer, similar to that of Intel Haswell and Broadwell processors.[33]

- Move elimination, a method that reduces physical data movement to reduce power consumption.

- Binary compatibility with Intel's Skylake (excluding VT-x and private MSRs):

- CLZERO instruction for clearing a cache line.[34] Useful for handling ECC-related Machine-check exceptions.

- PTE (page table entry) coalescing, which combines 4 kB page tables into 32 kB page size.

- "Pure Power" (more accurate power monitoring sensors).[35]

- Support for intel-style running average power limit (RAPL) measurement.[36]

- Smart Prefetch.

- Precision Boost.

- eXtended Frequency Range (XFR), an automated overclocking feature which boosts clock speeds beyond the advertised turbo frequency.[37]

This is the first time in a very long time that we engineers have been given the total freedom to build a processor from scratch and do the best we can do. It is a multi-year project with a really large team. It's like a marathon effort with some sprints in the middle. The team is working very hard, but they can see the finish line. I guarantee that it will deliver a huge improvement in performance and power consumption over the previous generation.

— Suzanne Plummer, Zen team leader, on September 19th, 2015.[38]

The Zen architecture is built on a 14 nanometer FinFET process subcontracted to GlobalFoundries,[39] which in turn licenses its 14 nm process from Samsung Electronics.[40] This gives greater efficiency than the 32 nm and 28 nm processes of previous AMD FX CPUs and AMD APUs, respectively.[41] The "Summit Ridge" Zen family of CPUs use the AM4 socket and feature DDR4 support and a 95 W TDP (thermal design power).[41] While newer roadmaps don't confirm the TDP for desktop products, they suggest a range for low-power mobile products with up to two Zen cores from 5 to 15 W and 15 to 35 W for performance-oriented mobile products with up to four Zen cores.[42]

Each Zen core can decode four instructions per clock cycle and includes a micro-op cache which feeds two schedulers, one each for the integer and floating point segments.[43][44] Each core has two address generation units, four integer units, and four floating point units. Two of the floating point units are adders, and two are multiply-adders. However, using multiply-add-operations may prevent simultaneous add operation in one of the adder units.[45] There are also improvements in the branch predictor. The L1 cache size is 64 KB for instructions per core and 32 KB for data per core. The L2 cache size 512 KB per core, and the L3 is 1–2 MB per core. L3 caches offer 5× the bandwidth of previous AMD designs.

History and development

[edit]AMD began planning the Zen microarchitecture shortly after re-hiring Jim Keller in August 2012.[46] AMD formally revealed Zen in 2015.

The team in charge of Zen was led by Keller (who left in September 2015 after a 3-year tenure) and Zen Team Leader Suzanne Plummer.[47][48] The Chief Architect of Zen was AMD Senior Fellow Michael Clark.[49][50][51]

Zen was originally planned for 2017 following the ARM64-based K12 sister core, but on AMD's 2015 Financial Analyst Day it was revealed that K12 was delayed in favor of the Zen design, to allow it to enter the market within the 2016 timeframe,[9] with the release of the first Zen-based processors expected for October 2016.[52]

In November 2015, a source inside AMD reported that Zen microprocessors had been tested and "met all expectations" with "no significant bottlenecks found".[2][53]

In December 2015, it was rumored that Samsung may have been contracted as a fabricator for AMD's 14 nm FinFET processors, including both Zen and AMD's then-upcoming Polaris GPU architecture.[54] This was clarified by AMD's July 2016 announcement that products had been successfully produced on Samsung's 14 nm FinFET process.[55] AMD stated Samsung would be used "if needed", arguing this would reduce risk for AMD by decreasing dependence on any one foundry.

In December 2019, AMD started putting out first generation Ryzen products built using the second generation Zen+ architecture.[56]

Advantages over predecessors

[edit]Manufacturing process

[edit]Processors based on Zen use 14 nm FinFET silicon.[57] These processors are reportedly produced at GlobalFoundries.[58] Prior to Zen, AMD's smallest process size was 28 nm, as utilized by their Steamroller and Excavator microarchitectures.[59][60] The immediate competition, Intel's Skylake and Kaby Lake microarchitecture, are also fabricated on 14 nm FinFET;[61] though Intel planned to begin the release of 10 nm parts later in 2017.[62] Intel was unable to reach this goal, and in 2021, only mobile chips have been produced with the 10nm process. In comparison to Intel's 14 nm FinFET, AMD claimed in February 2017 the Zen cores would be 10% smaller.[63] Intel has later announced in July 2018 that 10nm mainstream processors should not be expected before the second half of 2019.[64]

For identical designs, these die shrinks would use less current (and power) at the same frequency (or voltage). As CPUs are usually power limited (typically up to ~125 W, or ~45 W for mobile), smaller transistors allow for either lower power at the same frequency, or higher frequency at the same power.[65]

Performance

[edit]One of Zen's major goals in 2016 was to focus on performance per-core, and it was targeting a 40% improvement in instructions per cycle (IPC) over its predecessor.[66] Excavator, in comparison, offered 4–15% improvement over previous architectures.[67][68] AMD announced the final Zen microarchitecture actually achieved 52% improvement in IPC over Excavator.[69] The inclusion of SMT also allows each core to process up to two threads, increasing processing throughput by better use of available resources.

The Zen processors also employ sensors across the chip to dynamically scale frequency and voltage.[70] This allows for the maximum frequency to be dynamically and automatically defined by the processor itself based upon available cooling.

AMD has demonstrated an 8-core/16-thread Zen processor outperforming an equally-clocked Intel Broadwell-E processor in Blender rendering[4][10] and HandBrake benchmarks.[70]

Zen supports AVX2 but it requires two clock cycles to complete each AVX2 instruction compared to Intel's one.[71][72] This difference was corrected in Zen 2.

Memory

[edit]Zen supports DDR4 memory (up to eight channels)[73] and ECC.[74]

Pre-release reports stated APUs using the Zen architecture would also support High Bandwidth Memory (HBM).[75] However, the first demonstrated APU did not use HBM.[76] Previous APUs from AMD relied on shared memory for both the GPU and the CPU.

Power consumption and heat output

[edit]Processors built at the 14 nm node on FinFET silicon should show reduced power consumption and therefore heat over their 28 nm and 32 nm non-FinFET predecessors (for equivalent designs), or be more computationally powerful at equivalent heat output/power consumption.

Zen also uses clock gating,[44] reducing the frequency of underutilized portions of the core to save power. This comes from AMD's SenseMI technology, using sensors across the chip to dynamically scale frequency and voltage.[70]

Enhanced security and virtualization support

[edit]Zen added support for AMD's Secure Memory Encryption (SME) and AMD's Secure Encrypted Virtualization (SEV). Secure Memory Encryption is real-time memory encryption done per page table entry. Encryption occurs on a hardware AES engine and keys are managed by the onboard "Security" Processor (ARM Cortex-A5) at boot time to encrypt each page, allowing any DDR4 memory (including non-volatile varieties) to be encrypted. AMD SME also makes the contents of the memory more resistant to memory snooping and cold boot attacks.[77][78]

SME can be used to mark individual pages of memory as encrypted through the page tables. A page of memory that is marked encrypted will be automatically decrypted when read from DRAM and will be automatically encrypted when written to DRAM. The SME feature is identified through a CPUID function and enabled through the SYSCFG MSR. Once enabled, page table entries will determine how the memory is accessed. If a page table entry has the memory encryption mask set, then that memory will be accessed as encrypted memory. The memory encryption mask (as well as other related information) is determined from settings returned through the same CPUID function that identifies the presence of the feature.[79]

The Secure Encrypted Virtualization (SEV) feature allows the memory contents of a virtual machine (VM) to be transparently encrypted with a key unique to the guest VM. The memory controller contains a high-performance encryption engine which can be programmed with multiple keys for use by different VMs in the system. The programming and management of these keys is handled by the AMD Secure Processor firmware which exposes an API for these tasks.[80]

Connectivity

[edit]Incorporating much of the southbridge into the SoC, the Zen CPU includes SATA, USB, and PCI Express NVMe links.[81][82] This can be augmented by available Socket AM4 chipsets which add connectivity options including additional SATA and USB connections, and support for AMD's Crossfire and Nvidia's SLI.[83]

AMD, in announcing its Radeon Instinct line, argued that the upcoming Zen-based Naples server CPU would be particularly suited for building deep learning systems.[84][85] The 128[86] PCIe lanes per Naples CPU allows for eight Instinct cards to connect at PCIe x16 to a single CPU. This compares favorably to the Intel Xeon line, with only 40[citation needed] PCIe lanes.

Features

[edit]CPUs

[edit]This section is empty. You can help by adding to it. (March 2023) |

APUs

[edit]Products

[edit]The Zen architecture is used in the current-generation desktop Ryzen CPUs. It is also in Epyc server processors (successor of Opteron processors), and APUs.[75][unreliable source][87][88]

The first desktop processors without graphics processing units (codenamed "Summit Ridge") were initially expected to start selling at the end of 2016, according to an AMD roadmap; with the first mobile and desktop processors of the AMD Accelerated Processing Unit type (codenamed "Raven Ridge") following in late 2017.[89] AMD officially delayed Zen until Q1 of 2017. In August 2016, an early demonstration of the architecture showed an 8-core/16-thread engineering sample CPU at 3.0 GHz.[10]

In December 2016, AMD officially announced the desktop CPU line under the Ryzen brand for release in Q1 2017. It also confirmed Server processors would be released in Q2 2017, and mobile APUs in H2 2017.[90]

On March 2, 2017, AMD officially launched the first Zen architecture-based octacore Ryzen desktop CPUs. The final clock speeds and TDPs for the 3 CPUs released in Q1 of 2017 demonstrated significant performance-per-watt benefits over the previous K15h (Piledriver) architecture.[91][92] The octacore Ryzen desktop CPUs demonstrated performance-per-watt comparable to Intel's Broadwell octacore CPUs.[93][94]

In March 2017, AMD also demonstrated an engineering sample of a server CPU based on the Zen architecture. The CPU (codenamed "Naples") was configured as a dual-socket server platform with each CPU having 32 cores/64 threads.[4][10]

Desktop processors

[edit]Common features of Ryzen 1000 desktop CPUs:

- Socket: AM4.

- All the CPUs support DDR4-2666 in dual-channel mode.

- All the CPUs support 24 PCIe 3.0 lanes. 4 of the lanes are reserved as link to the chipset.

- No integrated graphics.

- L1 cache: 96 KB (32 KB data + 64 KB instruction) per core.

- L2 cache: 512 KB per core.

- Node/fabrication process: GlobalFoundries 14 LP.

| Branding and Model | Cores (threads) |

Clock rate (GHz) | L3 cache (total) |

TDP | Core config[i] |

Release date |

Launch price[a] | |||

|---|---|---|---|---|---|---|---|---|---|---|

| Base | PBO 1–2 (≥3) |

XFR[95] 1–2 | ||||||||

| Ryzen 7 | 1800X[96] | 8 (16) | 3.6 | 4.0 (3.7) |

4.1 | 16 MB | 95 W | 2 × 4 | March 2, 2017 | US $499 |

| PRO 1700X | 3.4 | 3.8 (3.5) |

3.9 | June 29, 2017 | OEM | |||||

| 1700X[96] | March 2, 2017 | US $399 | ||||||||

| PRO 1700 | 3.0 | 3.7 (3.2) |

3.75 | 65 W | June 29, 2017 | OEM | ||||

| 1700[96] | March 2, 2017 | US $329 | ||||||||

| Ryzen 5 | 1600X[97] | 6 (12) | 3.6 | 4.0 (3.7) |

4.1 | 95 W | 2 × 3 | April 11, 2017 | US $249 | |

| PRO 1600 | 3.2 | 3.6 (3.4) |

3.7 | 65 W | June 29, 2017 | OEM | ||||

| 1600[97] | April 11, 2017 | US $219 | ||||||||

| 1500X[97] | 4 (8) | 3.5 | 3.7 (3.6) |

3.9 | 2 × 2 | US $189 | ||||

| PRO 1500 | June 29, 2017 | OEM | ||||||||

| 1400[97] | 3.2 | 3.4 (3.4) |

3.45 | 8 MB | April 11, 2017 | US $169 | ||||

| Ryzen 3 | 1300X[98] | 4 (4) | 3.5 | 3.7 (3.5) |

3.9 | July 27, 2017 | US $129 | |||

| PRO 1300 | June 29, 2017 | OEM | ||||||||

| PRO 1200 | 3.1 | 3.4 (3.1) |

3.45 | |||||||

| 1200[98] | July 27, 2017 | US $109 | ||||||||

- ^ Manufacturer suggested retail price at launch

- ^ Core Complexes (CCX) × cores per CCX

Common features of Ryzen 1000 HEDT CPUs:

- Socket: TR4.

- All the CPUs support DDR4-2666 in quad-channel mode.

- All the CPUs support 64 PCIe 3.0 lanes. 4 of the lanes are reserved as link to the chipset.

- No integrated graphics.

- L1 cache: 96 KB (32 KB data + 64 KB instruction) per core.

- L2 cache: 512 KB per core.

- Node/fabrication process: GlobalFoundries 14LP.

| Branding and Model | Cores (threads) |

Clock rate (GHz) | L3 cache (total) |

TDP | Chiplets | Core config[i] |

Release date |

Launch price[a] | |||

|---|---|---|---|---|---|---|---|---|---|---|---|

| Base | PBO 1–4 (≥5) |

XFR[95] 1–2 | |||||||||

| Ryzen Threadripper |

1950X[99] | 16 (32) | 3.4 | 4.0 (3.7) |

4.2 | 32 MB | 180 W | 2 × CCD[ii] | 4 × 4 | August 10, 2017 | US $999 |

| 1920X[99] | 12 (24) | 3.5 | 4 × 3 | US $799 | |||||||

| 1900X[99] | 8 (16) | 3.8 | 4.0 (3.9) |

16 MB | 2 × 4 | August 31, 2017 | US $549 | ||||

- ^ Manufacturer suggested retail price at launch

- ^ Core Complexes (CCX) × cores per CCX

- ^ Processor package actually contains two additional inactive dies to provide structural support to the integrated heat spreader.

Desktop APUs

[edit]Ryzen APUs are identified by either the G or GE suffix in their name.

| Model | Release date & price |

Fab | Thermal Solution | CPU | GPU | Socket | PCIe lanes | DDR4 memory support |

TDP (W) | ||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Cores (threads) |

Clock rate (GHz) | Cache | Model | Config[i] | Clock (GHz) |

Processing power (GFLOPS)[ii] | |||||||||||

| Base | Boost | L1 | L2 | L3 | |||||||||||||

| Athlon 200GE[100] | September 6, 2018 US $55 |

GloFo 14LP |

AMD 65W thermal solution | 2 (4) | 3.2 | — | 64 KB inst. 32 KB data per core |

512 KB per core |

4 MB | Vega 3 | 192:12:4 3 CU |

1.0 | 384 | AM4 | 16 (8+4+4) | 2667 dual-channel |

35 |

| Athlon Pro 200GE[101] | September 6, 2018 OEM |

OEM | |||||||||||||||

| Athlon 220GE[102] | December 21, 2018 US $65 |

AMD 65W thermal solution | 3.4 | ||||||||||||||

| Athlon 240GE[103] | December 21, 2018 US $75 |

3.5 | |||||||||||||||

| Athlon 3000G[104] | November 19, 2019 US $49 |

1.1 | 424.4 | ||||||||||||||

| Athlon 300GE[105] | July 7, 2019 OEM |

OEM | 3.4 | ||||||||||||||

| Athlon Silver 3050GE[106] | July 21, 2020 OEM | ||||||||||||||||

| Ryzen 3 Pro 2100GE[107] | c. 2019

OEM |

3.2 | ? | ? | 2933 dual-channel | ||||||||||||

| Ryzen 3 2200GE[108] | April 19, 2018 OEM |

4 (4) | 3.2 | 3.6 | Vega 8 | 512:32:16 8 CU |

1126 | ||||||||||

| Ryzen 3 Pro 2200GE[109] | May 10, 2018 OEM | ||||||||||||||||

| Ryzen 3 2200G | February 12, 2018 US $99 |

Wraith Stealth | 3.5 | 3.7 | 45– 65 | ||||||||||||

| Ryzen 3 Pro 2200G[110] | May 10, 2018 OEM |

OEM | |||||||||||||||

| Ryzen 5 2400GE[111] | April 19, 2018 OEM |

4 (8) | 3.2 | 3.8 | RX Vega 11 | 704:44:16 11 CU |

1.25 | 1760 | 35 | ||||||||

| Ryzen 5 Pro 2400GE[112] | May 10, 2018 OEM | ||||||||||||||||

| Ryzen 5 2400G[113] | February 12, 2018[114][115] US $169 |

Wraith Stealth | 3.6 | 3.9 | 45– 65 | ||||||||||||

| Ryzen 5 Pro 2400G[116] | May 10, 2018 OEM |

OEM | |||||||||||||||

- ^ Unified Shaders : Texture Mapping Units : Render Output Units and Compute Units (CU)

- ^ Single-precision performance is calculated from the base (or boost) core clock speed based on a FMA operation.

Mobile APUs

[edit]| Model | Release date |

Fab | CPU | GPU | Socket | PCIe lanes |

Memory support |

TDP | ||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Cores (threads) |

Clock rate (GHz) | Cache | Model | Config[i] | Clock (MHz) |

Processing power (GFLOPS)[ii] | ||||||||||

| Base | Boost | L1 | L2 | L3 | ||||||||||||

| Athlon Pro 200U | 2019 | GloFo 14LP |

2 (4) | 2.3 | 3.2 | 64 KB inst. 32 KB data per core |

512 KB per core |

4 MB | Radeon Vega 3 | 192:12:4 3 CU |

1000 | 384 | FP5 | 12 (8+4) | DDR4-2400 dual-channel |

12–25 W |

| Athlon 300U | Jan 6, 2019 | 2.4 | 3.3 | |||||||||||||

| Ryzen 3 2200U | Jan 8, 2018 | 2.5 | 3.4 | 1100 | 422.4 | |||||||||||

| Ryzen 3 3200U | Jan 6, 2019 | 2.6 | 3.5 | 1200 | 460.8 | |||||||||||

| Ryzen 3 2300U | Jan 8, 2018 | 4 (4) | 2.0 | 3.4 | Radeon Vega 6 | 384:24:8 6 CU |

1100 | 844.8 | ||||||||

| Ryzen 3 Pro 2300U | May 15, 2018 | |||||||||||||||

| Ryzen 5 2500U | Oct 26, 2017 | 4 (8) | 3.6 | Radeon Vega 8 | 512:32:16 8 CU |

1126.4 | ||||||||||

| Ryzen 5 Pro 2500U | May 15, 2018 | |||||||||||||||

| Ryzen 5 2600H | Sep 10, 2018 | 3.2 | DDR4-3200 dual-channel |

35–54 W | ||||||||||||

| Ryzen 7 2700U | Oct 26, 2017 | 2.2 | 3.8 | Radeon RX Vega 10 | 640:40:16 10 CU |

1300 | 1664 | DDR4-2400 dual-channel |

12–25 W | |||||||

| Ryzen 7 Pro 2700U | May 15, 2018 | Radeon Vega 10 | ||||||||||||||

| Ryzen 7 2800H | Sep 10, 2018 | 3.3 | Radeon RX Vega 11 | 704:44:16 11 CU |

1830.4 | DDR4-3200 dual-channel |

35–54 W | |||||||||

- ^ Unified shaders : Texture mapping units : Render output units and Compute units (CU)

- ^ Single precision performance is calculated from the base (or boost) core clock speed based on a FMA operation.

Ultra-mobile APUs

[edit]Dalí

[edit]| Model | Release date |

Fab | CPU | GPU | Socket | PCIe lanes |

Memory support |

TDP | Part number | ||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Cores (threads) |

Clock rate (GHz) | Cache | Model | Config[a] | Clock (GHz) |

Processing power (GFLOPS)[b] | |||||||||||

| Base | Boost | L1 | L2 | L3 | |||||||||||||

| AMD 3020e | Jan 6, 2020 | 14 nm | 2 (2) | 1.2 | 2.6 | 64 KB inst. 32 KB data per core |

512 KB per core |

4 MB | Radeon Graphics (Vega) |

192:12:4 3 CU |

1.0 | 384 | FP5 | 12 (8+4) | DDR4-2400 dual-channel |

6 W | YM3020C7T2OFG |

| Athlon PRO 3045B | Q1 2021 | 2.3 | 3.2 | 128:8:4 2 CU |

1.1 | 281.6 | 15 W | YM3045C4T2OFG | |||||||||

| Athlon Silver 3050U | Jan 6, 2020 | YM3050C4T2OFG | |||||||||||||||

| Athlon Silver 3050C | Sep 22, 2020 | YM305CC4T2OFG | |||||||||||||||

| Athlon Silver 3050e | Jan 6, 2020 | 2 (4) | 1.4 | 2.8 | 192:12:4 3 CU[117] |

1.0 | 384 | 6 W | YM3050C7T2OFG | ||||||||

| Athlon PRO 3145B | Q1 2021 | 2.4 | 3.3 | 15 W | YM3145C4T2OFG | ||||||||||||

| Athlon Gold 3150U | Jan 6, 2020 | YM3150C4T2OFG | |||||||||||||||

| Athlon Gold 3150C | Sep 22, 2020 | YM315CC4T2OFG | |||||||||||||||

| Ryzen 3 3250U | Jan 6, 2020 | 2.6 | 3.5 | 1.2 | 460.8 | YM3250C4T2OFG | |||||||||||

| Ryzen 3 3250C | Sep 22, 2020 | YM325CC4T2OFG | |||||||||||||||

- ^ Unified shaders : Texture mapping units : Render output units and Compute units (CU)

- ^ Single precision performance is calculated from the base (or boost) core clock speed based on a FMA operation.

Pollock

[edit]| Model | Release date |

Fab | CPU | GPU | Socket | PCIe lanes |

Memory support |

TDP | Part number | ||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Cores (threads) |

Clock rate (GHz) | Cache | Model | Config[a] | Clock (GHz) |

Processing power (GFLOPS)[b] | |||||||||||

| Base | Boost | L1 | L2 | L3 | |||||||||||||

| AMD 3015e | Jul 6, 2020 | 14 nm | 2 (4) | 1.2 | 2.3 | 64 KB inst. 32 KB data per core |

512 KB per core |

4 MB | Radeon Graphics (Vega) |

192:12:4 3 CU |

0.6 | 230.4 | FT5 | 12 (8+4) | DDR4-1600 single-channel |

6 W | AM3015BRP2OFJ |

| AMD 3015Ce | Apr 29, 2021 | AM301CBRP2OFJ | |||||||||||||||

- ^ Unified shaders : Texture mapping units : Render output units and Compute units (CU)

- ^ Single precision performance is calculated from the base (or boost) core clock speed based on a FMA operation.

Embedded processors

[edit]V1000

[edit]In February 2018, AMD announced the V1000 series of embedded Zen+Vega APUs with four SKUs.[118]

| Model | Release date |

Fab | CPU | GPU | Memory support |

TDP | Junction temp. range (°C) | ||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Cores (threads) |

Clock rate (GHz) | Cache | Model | Config[i] | Clock (GHz) |

Processing power (GFLOPS)[ii] | |||||||||

| Base | Boost | L1 | L2 | L3 | |||||||||||

| V1202B | February 2018 | GloFo 14LP |

2 (4) | 2.3 | 3.2 | 64 KB inst. 32 KB data per core |

512 KB per core |

4 MB | Vega 3 | 192:12:16 3 CU |

1.0 | 384 | DDR4-2400 dual-channel |

12–25 W | 0–105 |

| V1404I | December 2018 | 4 (8) | 2.0 | 3.6 | Vega 8 | 512:32:16 8 CU |

1.1 | 1126.4 | -40–105 | ||||||

| V1500B | 2.2 | — | — | 0–105 | |||||||||||

| V1605B | February 2018 | 2.0 | 3.6 | Vega 8 | 512:32:16 8 CU |

1.1 | 1126.4 | ||||||||

| V1756B | 3.25 | DDR4-3200 dual-channel |

35–54 W | ||||||||||||

| V1780B | December 2018 | 3.35 | — | ||||||||||||

| V1807B | February 2018 | 3.8 | Vega 11 | 704:44:16 11 CU |

1.3 | 1830.4 | |||||||||

- ^ Unified Shaders : Texture Mapping Units : Render Output Units and Compute Units (CU)

- ^ Single-precision performance is calculated from the base (or boost) core clock speed based on a FMA operation.

R1000

[edit]In 2019, AMD announced the R1000 series of embedded Zen+Vega APUs.

| Model | Release date |

Fab | CPU | GPU | Memory support |

TDP | ||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Cores (threads) |

Clock rate (GHz) | Cache | Model | Config[i] | Clock (GHz) |

Processing power (GFLOPS)[ii] | ||||||||

| Base | Boost | L1 | L2 | L3 | ||||||||||

| R1102G | February 25, 2020 | GloFo 14LP |

2 (2) | 1.2 | 2.6 | 64 KB inst. 32 KB data per core |

512 KB per core |

4 MB | Vega 3 | 192:12:4 3 CU |

1.0 | 384 | DDR4-2400 single-channel |

6 W |

| R1305G | 2 (4) | 1.5 | 2.8 | DDR4-2400 dual-channel |

8-10 W | |||||||||

| R1505G | April 16, 2019 | 2.4 | 3.3 | 12–25 W | ||||||||||

| R1606G | 2.6 | 3.5 | 1.2 | 460.8 | ||||||||||

- ^ Unified Shaders : Texture Mapping Units : Render Output Units and Compute Units (CU)

- ^ Single-precision performance is calculated from the base (or boost) core clock speed based on a FMA operation.

Server processors

[edit]

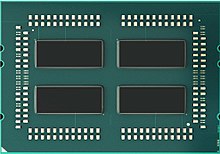

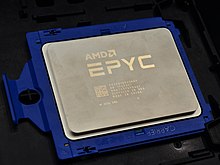

AMD announced in March 2017 that it would release a server platform based on Zen, codenamed Naples, in the second quarter of the year. The platform include 1- and 2-socket systems. The CPUs in multi-processor configurations communicate via AMD's Infinity Fabric.[119] Each chip supports eight channels of memory and 128 PCIe 3.0 lanes, of which 64 lanes are used for CPU-to-CPU communication through Infinity Fabric when installed in a dual-processor configuration.[120] AMD officially revealed Naples under the brand name Epyc in May 2017.[121]

On June 20, 2017, AMD officially released the Epyc 7000 series CPUs at a launch event in Austin, Texas.[122] Common features:

- SP3 socket

- Zen microarchitecture

- GloFo 14 nm process

- MCM with four System-on-a-chip (SOC) dies, two core complexes (CCX) per SOC die[123]

- Eight-channel DDR4-2666 (the 7251 model is limited to DDR4-2400)

- 128 PCIe 3.0 lanes per socket, 64 of which are used for Infinity Fabric in 2P platforms

- 7001P series models are restricted to uniprocessor operation (1P)

| Model[i] | Cores (threads) |

Chiplets | Core config[ii] |

Clock rate | Cache | TDP | Release | Embedded options[iii] | |||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Base (GHz) |

Boost (GHz) | L2 (per core) |

L3 (per CCX) |

Total | Date | Price | |||||||

| All–core | Max | ||||||||||||

| 7251[124][125] | 8 (16) | 4[123] | 8 × 1 | 2.1 | 2.9 | 2.9 | 512 KiB | 4 MiB | 36 MiB | 120 W | Jun 2017[126] | $475 | Yes |

| 7261[124][127] | 2.5 | 8 MiB | 68 MiB | 155/170 W | Jun 2018[128] | $570 | Yes | ||||||

| 7281[124][125] | 16 (32) | 8 × 2 | 2.1 | 2.7 | 2.7 | 4 MiB | 40 MiB | 155/170 W | Jun 2017[126] | $650 | Yes | ||

| 7301[124][125] | 2.2 | 8 MiB | 72 MiB | $800 | Yes | ||||||||

| 7351P[124][125] | 2.4 | 2.9 | 2.9 | $750 | 735P | ||||||||

| 7351[124][125] | $1,100 | Yes | |||||||||||

| 7371[124][129] | 3.1 | 3.6 | 3.8 | 200 W | Nov 2018[130] | $1,550 | Yes | ||||||

| 7401P[124][125] | 24 (48) | 8 × 3 | 2.0 | 2.8 | 3.0 | 8 MiB | 76 MiB | 155/170 W | Jun 2017[126] | $1,075 | 740P | ||

| 7401[124][125] | $1,850 | Yes | |||||||||||

| 7451[124][125] | 2.3 | 2.9 | 3.2 | 180 W | $2,400 | Yes | |||||||

| 7501[124][125] | 32 (64) | 8 × 4 | 2.0 | 2.6 | 3.0 | 8 MiB | 80 MiB | 155/170 W | $3,400 | Yes | |||

| 7551P[124][125] | 2.55 | 180 W | $2,100 | 755P | |||||||||

| 7551[124][125] | $3,400 | Yes | |||||||||||

| 7571[131][132] | 2.2 | 3.0 | 200 W | Nov 2018 | OEM/AWS | -- | |||||||

| 7601[124][125] | 2.7 | 3.2 | 180 W | Jun 2017[126] | $4,200 | Yes | |||||||

- ^ Models with "P" suffixes are uniprocessors, only available as single socket configuration.

- ^ Core Complexes (CCX) × cores per CCX

- ^ Epyc embedded 7001 series models have identical specifications as Epyc 7001 series.

Embedded server processors

[edit]In February 2018, AMD also announced the EPYC 3000 series of embedded Zen CPUs.[133]Common features of EPYC Embedded 3000 series CPUs:

- Socket: SP4 (31xx and 32xx models use SP4r2 package).

- All the CPUs support ECC DDR4-2666 in dual-channel mode (3201 supports only DDR4-2133), while 33xx and 34xx models support quad-channel mode.

- L1 cache: 96 KB (32 KB data + 64 KB instruction) per core.

- L2 cache: 512 KB per core.

- All the CPUs support 32 PCIe 3.0 lanes per CCD (max 64 lanes).

- Fabrication process: GlobalFoundries 14 nm.

| Model | Cores (threads) |

Clock rate (GHz) | L3 cache (total) |

TDP | Chiplets | Core config[i] |

Release date | ||

|---|---|---|---|---|---|---|---|---|---|

| Base | Boost | ||||||||

| All-core | Max | ||||||||

| 3101[134] | 4 (4) | 2.1 | 2.9 | 2.9 | 8 MB | 35 W | 1 × CCD | 1 × 4 | Feb 2018 |

| 3151[134] | 4 (8) | 2.7 | 16 MB | 45 W | 2 × 2 | ||||

| 3201[134] | 8 (8) | 1.5 | 3.1 | 3.1 | 30 W | 2 × 4 | |||

| 3251[134] | 8 (16) | 2.5 | 55 W | ||||||

| 3255[135] | 25–55 W | Dec 2018 | |||||||

| 3301[134] | 12 (12) | 2.0 | 2.15 | 3.0 | 32 MB | 65 W | 2 × CCD | 4 × 3 | Feb 2018 |

| 3351[134] | 12 (24) | 1.9 | 2.75 | 60–80 W | |||||

| 3401[134] | 16 (16) | 1.85 | 2.25 | 85 W | 4 × 4 | ||||

| 3451[134] | 16 (32) | 2.15 | 2.45 | 80–100 W | |||||

- ^ Core Complexes (CCX) × cores per CCX

See also

[edit]References

[edit]- ^ "AMD Ryzen™ 7 Desktop Processors Featuring Record-Breaking Overclocking Performance Available Worldwide Today" (Press release). Sunnyvale, California: Advanced Micro Devices, Inc. 2017-03-02. Archived from the original on 2021-10-28. Retrieved 2020-11-07.

- ^ a b c "GlobalFoundries announces 14nm validation with AMD Zen silicon". ExtremeTech. Archived from the original on 2016-12-07. Retrieved 2015-11-29.

- ^ Cutress, Ian (February 22, 2017). "AMD Launches Ryzen: 52% More IPC, Eight Cores for Under $330, Pre-order Today, On Sale March 2nd". AnandTech. Retrieved November 18, 2022.

- ^ a b c d e Anthony, Sebastian (18 August 2016). "AMD says Zen CPU will outperform Intel Broadwell-E, delays release to 2017". Ars Technica. Archived from the original on 18 August 2016. Retrieved 18 August 2016.

- ^ "Details of AMD Zen 16-core x86 APU emerge". 13 April 2015. Archived from the original on 2 May 2016. Retrieved 17 January 2016.

- ^ "AMD Zen-based 8-core Desktop CPU Arrives in 2016, on Socket FM3". TechPowerUp. Archived from the original on 2016-03-02. Retrieved 2016-01-17.

- ^ Kampman, Jeff (16 May 2017). "Ryzen Threadripper CPUs will offer 16 cores and 32 threads". Tech Report. Archived from the original on 17 May 2017. Retrieved 16 May 2017.

- ^ Kennedy, Patrick (16 May 2017). "AMD EPYC New Details on the Emerging Server Platform". Serve the Home. Archived from the original on 6 June 2017. Retrieved 16 May 2017.

- ^ a b Ryan Smith (6 May 2015). "AMD's 2016-2017 x86 Roadmap: Zen Is In, Skybridge Is Out". AnandTech. Archived from the original on 8 May 2015. Retrieved 15 May 2015.

- ^ a b c d Kampman, Jeff (18 August 2016). "AMD gives us our first real moment of Zen". Tech Report. Archived from the original on 18 November 2016. Retrieved 18 August 2016.

- ^ Cutress, Ian. "AMD's Future in Servers: New 7000-Series CPUs Launched and Epyc Analysis". AnandTech. Archived from the original on 21 June 2017. Retrieved 8 August 2017.

- ^ "HP ENVY x360 Convertible Laptop - 15z touch - HP® Official Store". store.hp.com. Archived from the original on 2017-12-10. Retrieved 2017-12-09.

- ^ Brad Chacos (8 January 2016). "AMD Zen-based CPUs and APUs will unify around Socket AM4". PCWorld. Archived from the original on 2 February 2017. Retrieved 10 January 2016.

- ^ "Ryzen™ Threadripper™ Processors | AMD". www.amd.com. Archived from the original on 2017-09-29. Retrieved 2017-09-29.

- ^ "How AMD's powerful Zen chip flouts the SoC stereotype". PCWorld. Archived from the original on 2017-02-06. Retrieved 2017-03-08.

- ^ Cutress, Ian (18 August 2016). "Early AMD Zen Server CPU and Motherboard Details". Anandtech. Archived from the original on 22 March 2017. Retrieved 22 March 2017.

- ^ AMD Shipped 260 Million Zen Cores by 2020 Archived 2021-10-29 at the Wayback Machine. AnandTech.

- ^ "AMD Reveals Why Threadripper CPUs Have 4 Dies Under the Hood - ExtremeTech". Archived from the original on 2020-11-02. Retrieved 2020-10-28.

- ^ "AMD Ryzen Threadripper Does Have Four 8-Core Dies (32-cores)". Archived from the original on 2018-07-02. Retrieved 2020-10-28.

- ^ Lilly, Paul (28 July 2017). "Overclocker delids an AMD Ryzen Threadripper chip and finds Epyc inside | PC Gamer". PC Gamer. Archived from the original on 2020-10-31. Retrieved 2020-10-28.

- ^ "Weekend tech reading: AMD 'Zen' and their return to high-end CPUs, tracking Windows pirates - TechSpot". techspot.com. Archived from the original on 2015-05-11. Retrieved 2015-05-12.

- ^ "AMD: Zen chips headed to desktops, servers in 2016 - The Tech Report - Page 1". techreport.com. 6 May 2015. Archived from the original on 2015-05-09. Retrieved 2015-05-12.

- ^ Anton Shilov (11 September 2014). "AMD: 'Bulldozer' was not a game-changer, but next-gen 'Zen' will be". KitGuru. Archived from the original on 4 June 2016. Retrieved 1 February 2015.

- ^ Software Optimization Guide for AMD Family 17h Processors Archived 2017-07-12 at the Wayback Machine / AMD, June 2017

- ^ "AMD Zen Confirmed for 2016, Features 40% IPC Improvement Over Excavator". Archived from the original on 2016-03-04. Retrieved 2016-01-11.

- ^ Ian Cutress (2017-03-02). "The Core Complex, Caches, and Fabric". Archived from the original on 2017-06-25. Retrieved 2017-06-21.

- ^ Clark, Mike. "A New x86 Core Architecture for the Next Generation of Computing" (PDF). AMD. p. 7. Archived (PDF) from the original on 2016-11-26.

- ^ Cutress, Ian. "AMD Zen Microarchitecture: Dual Schedulers, Micro-Op Cache and Memory Hierarchy Revealed". Archived from the original on 2016-08-19. Retrieved 2016-08-18.

- ^ Mujtaba, Hassan (23 August 2016). "AMD Opens The Lid on Zen Architectural Details at Hot Chips – Huge Performance Leap Over Excavator, Massive Throughput on 14nm FinFET Design". WCCFtech. Archived from the original on 25 August 2016. Retrieved 23 August 2016.

- ^ Walrath, Josh (2 March 2017). "AMD Zen Architecture Overview: Focus on Ryzen | PC Perspective". PC Perspective. Archived from the original on 12 October 2017. Retrieved 13 March 2017.

- ^ Jiménez, Daniel. "Strided Sampling Hashed Perceptron Predictor" (PDF). Texas A&M University. Archived (PDF) from the original on 2016-09-19. Retrieved 2016-08-23.

- ^ Williams, Chris. "'Neural network' spotted deep inside Samsung's Galaxy S7 silicon brain". The Register. Archived from the original on 2017-09-19. Retrieved 2017-09-19.

- ^ Fog, Agner. "The microarchitecture of Intel, AMD and VIA CPUs" (PDF). Technical University of Denmark. Archived (PDF) from the original on 2017-03-28. Retrieved 2016-08-23.

- ^ a b c "AMD Starts Linux Enablement On Next-Gen "Zen" Architecture". Phoronix. 17 March 2015. Archived from the original on 8 March 2017. Retrieved 17 March 2015.

- ^ "AMD Takes Computing to a New Horizon with Ryzen™ Processors". www.amd.com. Archived from the original on 2018-06-12. Retrieved 2017-09-19.

- ^ "Linux support for Power Measurement Interfaces". web.eece.maine.edu. Archived from the original on 2018-04-05. Retrieved 2020-11-25.

- ^ Chen, Sam (24 June 2017). "XFR". Custom PC Review. Archived from the original on 26 August 2018. Retrieved 26 July 2017.

- ^ Kirk Ladendorf - For the American-Statesman. "Amid challenges, chipmaker AMD sees a way forward".

- ^ Lilly, Paul (23 July 2016), "AMD Shipping Zen In Limited Quantity Q4, Volume Rollout Ramps Q1 2017", hothardware.com, archived from the original on 21 April 2019, retrieved 19 August 2016,

Zen is being built on an advanced GlobalFoundries-sourced 14nm FinFET process

- ^ Schor, David (2018-07-22). "VLSI 2018: GlobalFoundries 12nm Leading-Performance, 12LP". WikiChip Fuse. Archived from the original on 2019-04-07. Retrieved 2019-05-31.

- ^ a b "14nm AMD Zen CPU Will Have DDR4 and Simultaneous Multithreading". Softpedia. 28 January 2015. Archived from the original on 10 March 2015. Retrieved 31 January 2015.

- ^ "AMD's next gen CPU Zen". Shattered.Media. May 2015. Archived from the original on 2015-11-17.

- ^ "AMD's Zen core (family 17h) to have ten pipelines per core". 3 October 2015. Archived from the original on 2015-10-29. Retrieved 2015-10-13.

- ^ a b Cutress, Ian (18 August 2016). "AMD Zen Microarchitecture". Anandtech. Archived from the original on 19 August 2016. Retrieved 18 August 2016.

- ^ AMD, "Software Optimization Guider for AMD Family 17h Processors"

- ^ Jim Keller On AMD's Next-Gen High Performance x86 Zen Core & K12 ARM Core. YouTube. 7 May 2014.

- ^ "Jim Keller Leaves AMD". Anand tech. Archived from the original on 2015-10-15. Retrieved 2015-10-14.

- ^ Ladendorf, Kirk. "Amid challenges, chipmaker AMD sees a way forward". Austin American-Statesman. Archived from the original on 2020-01-04. Retrieved 2020-01-04.

- ^ Merritt, Rick (24 August 2016). "AMD Reveals Zen of X86". EE Times. Archived from the original on 4 March 2017. Retrieved 3 March 2017.

- ^ TAKAHASHI, Dean (24 August 2016). "How AMD designed what could be its most competitive processors in a decade". VentureBeat. Archived from the original on 4 March 2017. Retrieved 3 March 2017.

- ^ Wong, Adrian (18 April 2017). "Joe Macri : The Disruptive Nature of AMD Ryzen". TechArp. Archived from the original on 22 April 2017. Retrieved 20 April 2017.

- ^ "AMD set to release first 'Zen'-based microprocessors in late 2016 – document". KitGuru.net. 12 June 2015. Archived from the original on 13 September 2015. Retrieved 30 August 2015.

- ^ "OC3D :: Article :: AMD Tests Zen CPUs, "Met All Expectation" with no "Significant Bottlenecks" found :: AMD Tests Zen CPUs, Met All Expectation with no Significant Bottlenecks found". 2 November 2015. Archived from the original on 2015-11-04. Retrieved 2015-11-03.

- ^ "Samsung to fab AMD Zen & Arctic islands on its 14 nm Finfet node", Tech power up, archived from the original on 2016-01-09, retrieved 2016-01-10.

- ^ Moorhead, Patrick (25 July 2016). "AMD Officially Diversifies 14nm Manufacturing With Samsung". Forbes. Archived from the original on 26 July 2016. Retrieved 26 July 2016.

- ^ "First-Gen AMD Ryzen CPUs are Appearing with 12nm Zen+ Architecture". 2019-12-22. Archived from the original on 2019-12-22. Retrieved 2019-12-22.

- ^ "AMD's next-gen CPU leak: 14nm, simultaneous multithreading, and DDR4 support". ExtremeTech. Archived from the original on 2016-01-25. Retrieved 2016-01-12.

- ^ Rulison, Larry (22 August 2016). "Reports: Chip made by GlobalFoundries beats Intel". Times Union. Archived from the original on 23 August 2016. Retrieved 22 August 2016.

- ^ "AMD: We have taped out our first FinFET products". KitGuru. Archived from the original on 2016-01-25. Retrieved 2016-01-10.

- ^ "CES: AMD finally unveils 28nm APU Kaveri to battle Intel Haswell". The Inquirer. Archived from the original on January 9, 2014.

{{cite web}}: CS1 maint: unfit URL (link) - ^ "Intel Kaby Lake to compete against AMD Zen at end of 2016". 2016-03-02. Archived from the original on 2016-03-06. Retrieved 2016-03-07.

Intel's Kaby Lake-series processors, which are scheduled to launch in the third quarter, but will not begin volume production until the end of 2016, while AMD is set to release its Zen architecture-based processors at the end of the fourth quarter.

- ^ Edward Jones (21 Oct 2016). "AMD Zen: A serious challenge to Intel?". Channel Pro. Archived from the original on 23 June 2016. Retrieved 27 June 2016.

- ^ Manion, Wayne (8 February 2017). "AMD touts Zen die size advantage at ISSCC". Tech Report. Archived from the original on 9 February 2017. Retrieved 10 February 2017.

- ^ "Intel says not to expect mainstream 10nm chips until 2H19 | Ars Technica". 27 July 2018. Archived from the original on 2018-07-29. Retrieved 2018-07-29.

- ^ "Intel's 'Tick-Tock' Seemingly Dead, Becomes 'Process-Architecture-Optimization'". Anandtech. Archived from the original on 23 March 2016. Retrieved 23 March 2016.

- ^ Smith, Ryan (31 May 2016). "AMD Briefly Shows Off Zen "Summit Ridge" Silicon". Archived from the original on 5 June 2016. Retrieved 7 June 2016.

- ^ "AMD Announces Zen, 40% IPC Improvement Over Excavator - Coming In 2016". 7 May 2015. Archived from the original on 5 June 2016. Retrieved 4 June 2016.

- ^ Ian Cutress (June 2, 2015). "IPC Increases: Double L1 Data Cache, Better Branch Prediction - AMD Launches Carrizo: The Laptop Leap of Efficiency and Architecture Updates". Anandtech. Archived from the original on February 16, 2016. Retrieved January 17, 2016.

- ^ Cutress, Ian (22 February 2017). "AMD Launches Zen". Anandtech.com. Archived from the original on 27 February 2017. Retrieved 22 February 2017.

- ^ a b c Kampman, Jeff (13 December 2016). "AMD crests Summit Ridge with Ryzen CPUs". TechReport. Archived from the original on 14 December 2016. Retrieved 13 December 2016.

- ^ Cutress, Ian. "AMD Zen Microarchiture Part 2: Extracting Instruction-Level Parallelism". Archived from the original on 2017-03-12. Retrieved 2017-03-10.

- ^ Leadbetter, Richard (22 February 2017). "In Theory: How AMD's Ryzen will disrupt the gaming CPU market". Eurogamer. Archived from the original on 9 March 2017. Retrieved 10 March 2017.

- ^ "AMD's Zen processors to feature up to 32 cores, 8-channel DDR4". TechSpot. Archived from the original on 2016-02-28. Retrieved 2016-02-24.

- ^ MAC (30 March 2017). "ECC Memory & AMD's Ryzen - A Deep Dive". Hardware Canucks. Archived from the original on 4 July 2017. Retrieved 14 July 2017.

- ^ a b "Zen-based APU with HBM to be AMD Carrizo successor". 4 January 2016. Archived from the original on 2016-01-12. Retrieved 2016-01-10.

- ^ Shrout, Ryan (30 May 2017). "Computex 2017: AMD Demos Ryzen Mobile SoC with Vega Graphics". PC Perspective. Archived from the original on 22 March 2019. Retrieved 2 June 2017.

- ^ "[RFC PATCH v1 00/18] x86: Secure Memory Encryption (AMD)". Archived from the original on 2016-05-01. Retrieved 2016-05-09.

- ^ "AMD MEMORY ENCRYPTION WHITEPAPER" (PDF). Archived (PDF) from the original on 2016-05-09. Retrieved 2016-05-09.

- ^ "LKML - Tom Lendacky (AMD) explains AMD Secure Memory Encryption". Archived from the original on 2016-08-04. Retrieved 2016-05-09.

- ^ "AMD - Other Developer Guides: Secure Encrypted Virtualization Key Management PDF – 05/19/2016" (PDF). Archived (PDF) from the original on 2017-03-25. Retrieved 2017-06-14.

- ^ L, Alex; Walrath, Josh (12 January 2017). "Podcast #432 - Kaby Lake, Vega, CES Review". PC Perspective. Retrieved 13 January 2017.

- ^ Mah Ung, Gordon (28 September 2016). "How AMD's powerful Zen chip flouts the SoC stereotype". PC World. Archived from the original on 6 February 2017. Retrieved 13 January 2017.

- ^ Justin, Michael; Sexton, Allen (3 March 2017). "AMD's AM4 Ryzen Chipsets". Tom's Hardware. Retrieved 3 March 2017.

- ^ Smith, Ryan (12 December 2016). "AMD Announces Radeon Instinct: GPU Accelerators for Deep Learning, Coming in 2017". Anandtech. Archived from the original on 12 December 2016. Retrieved 12 December 2016.

- ^ Shrout, Ryan (12 December 2016). "Radeon Instinct Machine Learning GPUs include Vega, Preview Performance". PC Per. Archived from the original on 11 August 2017. Retrieved 12 December 2016.

- ^ Mujtaba, Hassan (2017-03-07). "AMD Naples High-Performance Server Chips With 32 Cores, 64 Threads Detailed". Wccftech. Archived from the original on 2018-11-24. Retrieved 2018-11-24.

- ^ "AMD Zen FX CPUs, APUs Release Details Surface, Top-Notch Performance In The Cards". Tech Times. Archived from the original on 2015-12-25. Retrieved 2016-01-10.

- ^ "32-core AMD Opteron to feature quad-die MCM design". KitGuru. Archived from the original on 2016-01-25. Retrieved 2016-01-10.

- ^ Mark Mantel (7 February 2017). "CPU-Roadmap 2017 - 2018: Künftige AMD- und Intel-CPUs/-APUs in der Übersicht". PC Games Hardware (in German). Archived from the original on 1 March 2017. Retrieved 7 February 2017.

- ^ Larabel, Michael (13 December 2016). "AMD Reveals More Zen CPU Details, Officially Known As Ryzen, No Linux Details Yet". Phoronix. Archived from the original on 14 December 2016. Retrieved 13 December 2016.

- ^ "Power Consumption And Efficiency - AMD FX-8350 Review: Does Piledriver Fix Bulldozer's Flaws?". Tom's Hardware. 2012-10-22. Retrieved 2017-03-12.

- ^ "AMD Ryzen 7 1800X: Power Consumption And Temperatures". Tom's Hardware. 2017-03-02. Retrieved 2017-03-12.

- ^ "AMD Ryzen 7 1800X and AM4 Platform Review". bit-tech. Archived from the original on 2017-03-13. Retrieved 2017-03-12.

- ^ "The AMD Ryzen 7 1800X Review: Now and Zen | Power Consumption and Conclusions". www.pcper.com. 2 March 2017. Archived from the original on 2017-07-03. Retrieved 2017-03-12.

- ^ a b Chen, Sam (February 13, 2020). "What is XFR? (AMD)". Gear Primer. Retrieved June 11, 2020.

- ^ a b c Safford, Matt. "AMD Ryzen 7 1700X Review". PCMAG. Retrieved 14 May 2024.

- ^ a b c d Wan, Samuel (5 April 2017). "AMD Ryzen 5 1600 Review Pops Up Ahead of Launch". eTeknix. Retrieved 14 May 2024.

- ^ a b Hagedoorn, Hilbert (27 July 2017). "AMD Ryzen 3 1200 and 1300X review". www.guru3d.com. Retrieved 14 May 2024.

- ^ a b c Ung, Gordon Mah (6 September 2017). "AMD Ryzen Threadripper: Everything we know so far about this monster CPU". PCWorld. Retrieved 14 May 2024.

- ^ "AMD Athlon 200GE Processor with Radeon Vega 3 Graphics". AMD.

- ^ "AMD Athlon PRO 200GE APU". AMD.

- ^ "AMD Athlon 220GE Processor with Radeon Vega 3 Graphics".

- ^ "AMD Athlon 240GE Processor with Radeon Vega 3 Graphics". AMD.

- ^ "AMD Athlon 3000G Processor with Radeon Graphics". AMD.

- ^ "AMD Athlon 300GE".

- ^ "AMD Athlon Silver 3050GE".

- ^ "HP Desktop Pro A G2 Specifications". Hewlett-Packard.

- ^ "AMD Ryzen 3 2200GE Processor with Radeon Vega 8 Graphics".

- ^ "AMD Ryzen 3 PRO 2200GE Processor with Radeon Vega 8 Graphics".

- ^ "AMD Ryzen 3 PRO 2200G Processor with Radeon Vega 8 Graphics". www.amd.com.

- ^ "Specs". www.amd.com. Retrieved 2019-06-10.

- ^ "Specs". www.amd.com. Retrieved 2019-06-10.

- ^ "AMD Ryzen 5 2400G". Retrieved 2018-01-19.

- ^ "AMD's 2nd-gen Ryzen is coming in April, desktop Ryzen APUs arrive February 12". TechSpot. Retrieved 2019-06-10.

- ^ Peter Bright (2018-01-08). "AMD's 2018 roadmap: Desktop APUs in February, second-generation Ryzen in April". Ars Technica. Retrieved 2019-06-10.

- ^ "Specs". www.amd.com. Retrieved 2019-06-10.

- ^ "AMD Radeon Vega 3 Mobile Specs". TechPowerUp. Retrieved April 25, 2023.

- ^ Alcorn, Paul (21 February 2018). "AMD Launches Ryzen Embedded V1000, EPYC Embedded 3000 Processors". Tom's Hardware. Retrieved 5 April 2018.

- ^ Kampman, Jeff (7 March 2017). "AMD's Naples platform prepares to take Zen into the datacenter". Tech Report. Archived from the original on 18 August 2017. Retrieved 7 March 2017.

- ^ Cutress, Ian (7 March 2017). "AMD Prepares 32-Core Naples CPUs for 1P and 2P Servers: Coming in Q2". Anandtech. Archived from the original on 11 September 2017. Retrieved 7 March 2017.

- ^ Kampman, Jeff (16 May 2017). "AMD's Naples datacenter CPUs will make an Epyc splash". Tech Report. Archived from the original on 17 May 2017. Retrieved 16 May 2017.

- ^ "AMD launches broad Epyc server processor line with up to 32 cores per chip". VentureBeat. 2017-06-20. Archived from the original on 2017-08-08. Retrieved 2017-08-08.

- ^ a b ""Zeppelin": An SoC for Multichip Architectures". 26 October 2018. Retrieved Sep 27, 2024.

- ^ a b c d e f g h i j k l m n "AMD EPYC 7000 Series Processors" (PDF). AMD. January 2019. Retrieved March 25, 2023.

- ^ a b c d e f g h i j k l Cutress, Ian (June 20, 2017). "AMD's Future in Servers: New 7000-Series CPUs Launched and EPYC Analysis". AnandTech. Retrieved June 21, 2017.

- ^ a b c d Kennedy, Patrick (May 16, 2017). "AMD EPYC New Details on the Emerging Server Platform". ServeTheHome. Retrieved May 16, 2017.

- ^ "AMD EPYC 7261 - PS7261BEV8RAF". CPU-World. March 26, 2023.

- ^ Kennedy, Patrick (October 31, 2018). "AMD EPYC 7261 8 Core CPU Quietly Launched L3 Cache Monster". ServeTheHome. Retrieved March 28, 2023.

- ^ "AMD EPYC 7371 - PS7371BDVGPAF". CPU-World. March 26, 2023.

- ^ "New AMD-Powered Supercomputers Unleash Discovery and Accelerate Innovation" (Press release). AMD. November 13, 2018. Retrieved March 28, 2023.

- ^ "AMD EPYC 7571 - PS7571BDVIHAF". CPU-World. March 25, 2023.

- ^ Larabel, Michael (November 7, 2018). "A Look At The AMD EPYC Performance On The Amazon EC2 Cloud". Phoronix. Retrieved March 28, 2023.

- ^ Alcorn, Paul (21 February 2018). "AMD Launches Ryzen Embedded V1000, EPYC Embedded 3000 Processors". Tom's Hardware. Retrieved 5 April 2018.

- ^ a b c d e f g h "Product Brief: AMD EPYC Embedded 3000 Family" (PDF). AMD. 2018. Retrieved March 26, 2023.

- ^ "AMD EPYC Embedded 3255 - PE3255BGR88AF". CPU-World. March 26, 2023.

External links

[edit]- Ryzen Processors – AMD