V850

| |

| General information | |

|---|---|

| Launched | 1994 |

| Discontinued | current |

| Common manufacturer |

|

| Performance | |

| Max. CPU clock rate | 32 kHz to 320 MHz |

| Data width | 32 |

| Address width | 32 |

| Cache | |

| L1 cache | configurable |

| Architecture and classification | |

| Application | Embedded, Mobile equipment, Air conditioner, Automotive |

| Technology node | 0.8 μm to 40 nm |

| Microarchitecture | V810 (1991), V850 (1994), V850E (1996), V850E1 (1999), V850ES (2002), V850E2 (2004), V850E1F (2005), V850E2v2 (FIX ME), V850E2v3 (2009), V850E2v4 (2010), V850E2v3S (2011), V850E3v5 (2014) |

| Instruction set | V800 Series |

| Extensions |

|

| Number of instructions | v850: 74 v850e: 81 v850e1: 80 (83) v850e1f: 96 v850e2: 89 v850e2v3: 98 V850e3v5: FIX ME |

| Physical specifications | |

| Cores |

|

| Products, models, variants | |

| Product code names |

|

| Variant |

|

| History | |

| Predecessor | "V80" CISC core |

V850 is a 32-bit RISC CPU architecture produced by Renesas Electronics for embedded microcontrollers. It was designed by NEC as a replacement for their earlier NEC V60 family, and was introduced shortly before NEC sold their designs to Renesas in the early 1990s. It has continued to be developed by Renesas as of 2018[update].

The V850 architecture is a load/store architecture with 32 32-bit general-purpose registers. It features a compressed instruction set with the most frequently used instructions mapped onto 16-bit half-words.

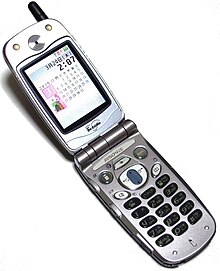

Intended for use in ultra-low power consumption systems, such as those using 0.5 mW/MIPS, the V850 has been widely used in a variety of applications, including optical disk drives, hard disk drives, mobile phones, car audio, and inverter compressors for air conditioners. Today, microarchitectures primarily focus on high performance and high reliability, such as the dual-lockstep redundant mechanism for the automotive industry; and the V850 and RH850 families are comprehensively used in cars.

The V850/RH850 microcontrollers are also used prominently on non-Japanese automobile marques such as Chevrolet, Chrysler, Dodge, Ford, Hyundai, Jeep, Kia, Opel, Range Rover, Renault and Volkswagen Group brands.

Overview

[edit]The V850 is the trademark name for a 32-bit RISC CPU architecture for embedded microcontrollers of Renesas Electronics Corporation. It was originally developed and manufactured by NEC Corporation in the early 1990s[1][2] (the copyright mark for the microcode on the package shows 1991) as a branch of the V800 Series[3]: 97, PDF103 and is still being evolved today.[4]

Its base-architecture has been succeeded by the V850 family variants, named V850E, V850E1, V850ES,[5] V850E1F, V850E2, V850E2M, V850E2S, and the RH850 family (V850E2M, V850E2S, and V850E3) CPU cores.

Many compilers and debuggers are available from various development tool vendors.

Real-time operating systems are provided by compiler vendors.

In-circuit emulators (ICE) are provided by many vendors. Legacy proven pod-based types—the JTAG-based N-Wire interface with the N-trace type, and the Nexus interface with the Aurora Trace type—are available.

Application systems

[edit]

The first V850 CPU core was used in many DVD drives manufactured by NEC's and Sony's Optiarc (later wholly owned by Sony).[6][7] NEC Electronics (currently Renesas Electronics) itself intensively developed application-specific standard products (ASSPs) for SCOMBO Series optical disk drives.[8][9] This first generation of processor core was also used for hard disk drives manufactured by Quantum Corporation (see photo).

In 1997, the V850/xxn product line started with the V850/SA1[10] and the V850/SV1[11] and expanded its application to ultra-lo-power products such as "handy camcorders." It has a main and sub internal oscillator amplifier working from 1.8 V to 3.6 V with external crystal or ceramic resonator.[10] Software STOP mode, whose internal watch timer operates with a 32.768 kHz sub-oscillator, typically consumes only 8μA of electrical current.[12][13] In 1998, NEC launched the V850/SB1,[14] with IEBus controller, for car audio, an ultra-low-power (3.6 mW@5 V/MIPS) and ultra-low-noise (EMI/EMS) 5 V product.[15] The V850/SC1[16] was also for car audio.[17] These strategic product line expansions succeeded in increasing the number of devices sold.

This first generation of the V850 core is also used for some NEC mobile phones.[18] It is also used for the programmable-host CPUs of some small form factor GSM/GPRS mobile devices with GPS embedded modem modules.[19]

In the next phase, NEC targeted the automotive industry with a CAN bus controller based on the V850,[20] as the V850/SF1.[21] Later on, the automotive industry became the main target of the V850 and RH850.

The V850E core was targeted at system-on-a-chip (SoC) applications as well as standard products,[22][23] and was used for some Japanese domestic mobile phones, including Sony Mobile's and NEC's.[24][25][26][27][28] V850E and V850ES are also used in air conditioning inverter compressors.[29][30][31][32] At this stage, another mass market was its use in car audio.[33] The V850ES core succeeded in the low-power embedded-product line,[34] and is ISA-compatible with the V850E. NEC Electronics (currently, Renesas Electronics) adopted the V850 CPU core for its USB 3.0 controllers.[35]: 11

Around 2005, several companies started a feasibility study for the FlexRay controller on the V850E platform. Yokogawa Digital Computer (currently DTS INSIGHT) developed an evaluation board named GT200 with a V850E/IA1 and a field-programmable gate array (FPGA), which employs the FlexRay controller developed by Bosch.[36]: 78, PDF80

The V850E2 core primarily targeted automotive areas,[37] but was also used for NEC's mobile phones.[38]

The V850 family line up (based on V850E, V850ES, and V850E2 cores) and the Renesas RH850 family (based on the V850E3 core, as of 2018) are mainly employed in automotive applications as well as inter-equipment connectivity and motor-control specific microcontroller units (MCUs).[39][40]

Trademark strategy

[edit]The V850 is a unregistered trademark but not a registered one.[41] NEC once applied for a trademark to be registered with the Japan Patent Office, but it was rejected,[42][43] as it was a natural extension of the series number. However, this action has been enough to prevent other people or organizations from registering it as a trademark. In addition, Renesas has been using the V850X/xxn type trademark, such as V850E/MA1, for more than 20 years, because the combination of one alphabetical with two numerical characters cannot be granted as a registered trademark. It is thus free to use without registration.

One exception is V850E/PHO3 (PHOENIX 3, or PHOENIX-FS).[44]: 3 [45]: 33 Another usage of PHOENIX 3 by Renesas Electronics is the COOL PHOENIX 3, which employs the ARM Cortex-M0 core.[46] PHOENIX 3 is a registered trademark of the 3DO Company as USPTO Reg. 2,009,119.[47]

According to current Renesas Electronics documentation, at least the following strings are regarded as its trademark: "V800 Series", "V850 family", "V850/SA1", "V850/SB1", "V850/SB2", "V850/SF1", "V850/SV1", "V850E/MA1", "V850E/MA2", "V850E/IA1", "V850E/IA2", "V850E/MS1", "V850E/MS2", "V851", "V852", "V853", "V854", "V850", "V850E", and "V850ES".[41][48]

Because the V850 trademark has been used for more than 20 years, most people do not know that the RH850 family is based on an extension of the V850 instruction set architecture, and has backward compatibility with V850, V850E, V850ES, and V850E2. The RH850 is consequently thought of as being without the legacy software compatibility of the V850.[49][50]

Development methodology

[edit]

Marked as "©NEC 1991."

Because the V850 family[48]: 16 was developed as a branch of the V800 series,[3]: 97, PDF103 the basic CPU architecture is inherited from the V810.[52] The instruction set architecture of the first V850 is drastically modified from that of the V810, but the difference is within a patch level from the GNU Compiler Collection point of view.[53] The main purpose of this change is to implement saturation arithmetic at customers' request.

The detailed design methodology of the V810 is described in this journal.[56] The V850 utilizes these design assets; but the datapath logic was changed from dynamic logic to static logic, to enable 32.768 kHz real-time clock frequency operation mode.

The register-transfer level "CPU architecture design" of the V810 is developed with the Functional Description Language (FDL)[57][58][59] on the Falcon Simulator software, which are NEC's in-house CAD tools. This methodology is the same as that used for the NEC V60.[60] In the late 1980s, the Verilog HDL had not yet been acquired by Cadence Design Systems.[61] FDL had been used until the middle of the 2000s, and was also used for the development of NEC's super-computer named Earth Simulator.[62]

The difference from V60 is that the circuit diagram was written with a schematic editor, not of Calma but of Mentor Graphics, called NETED,[63] a part of the Design Architect product[64][65] on Apollo Computer's workstation, which was the major schematic editor at that moment.[66] It enabled designers to generate netlists, such as EDIF and SPICE, for LVS programs like cadence's Dracula products, and NEC's in-house Zycad netlist for logic simulation. Later on, this circuit diagram of NETED was able to generate a gate-level Verilog HDL netlist for V850.

Most of the register-transfer-level FDL netlist was translated to the gate-level schematic by hand, because the logic synthesis had not yet to be practical. The FDL was precisely divided into datapath and random logic. For the datapath part, the gate-level circuit diagram enabled manually repeated artwork. On the other hand, for the random logic part, logic synthesis was tried for generating gate-level schematic, but it was only about 10% of the total circuit.

In addition, formal verification was also not yet practical, which meant that full regression test by dynamic logic simulation was required for the gate-level netlist to compare with the RTL one. For gate-level logic simulation, NEC's in-house CAD tool V-SIM was usually used.[67] But sometimes a hardware emulator, such as Zycad LE simulation accelerator,[68] was used for this purpose. (Refer to:.[69]: 13 In this material, the performance of Zycad LE is compared with NEC's HAL, but initial design decade differs.[70])

Architecture

[edit]Basic architecture

[edit]The basis of the V810 and V850 has a typical general-purpose registers-based load/store architecture.[71]: 4

There are 32 32-bit general-purpose registers. Register 0 (R0) is fixed as the Zero Register which always contains zero.

In the V850, R30 is implicitly used by the sld and sst instructions. 16-bit short-format load/store instructions use element pointer (ep), where the addressing mode comprises the base address register ep and immediate-operand offsets.

In V850E or later microarchitectures, R3 is implicitly used by PREPARE/DISPOSE; call stack frame creation; and unwinding instructions, as a stack pointer. Compilers' calling conventions also use R3 as the stack pointer.

The original V850 has a simple 5-stage 1-clock pitch pipeline architecture.[48]: 114–126 This is a significant feature of reduced instruction set computers (RISCs). But the object-code size is about half that of the MIPS R3000,[71]: 5 because the V810 and V850 adopted 16-bit and 32-bit 2-way form-length instruction formats, respectively,[48]: 38–40 [71]: 17 [72]: 29–30 and most of the frequently used instructions are mapped onto a 16-bit half-word. In other words, a 16-bit external bus width is enough to provide instructions continuously without pipeline stalling, which enables low power consumption on the application board, and is suitable for mobile equipment. This concept is similar to Renesas (formerly, Hitachi) SH, ARM Thumb, and MIPS16 instruction set architectures.[73]: 4

In addition, the instruction set is carefully implemented. For example, to execute a function call with a Jump and (Register) Link instruction,[48]: 61 [71]: 20 [72]: 64 which saves the next program counter (PC) on a register (fixed to R31 in V810), is also one of the RISC techniques to reduce the number of instructions. Return from the function can be accoomplished by jmp [Rn] (jmp [R31] in V810) instruction.[48]: 61 [71]: 23 [72]: 65 Typical CISC processors use call and return instructions and push the next PC on their stack memory area.

But V810 and V850 have some microarchitecture differences. The V810 adopts a microprogram operation method for some instructions, such as floating-point arithmetic and bit string operations, while the V850 uses a one-hundred-percent hardwired control method. As a result, for example, the first V850 does not have floating-point arithmetic and bit manipulation instruction sets, including the "find first one/zero" (search 1/0; SCH1x/SCH0x), except for "set/clr/negate a bit" (SET1/CLR1/NOT1). Those extended instruction sets are revived in V850E2x extensions.

Though the V800 series adopts a RISC instruction set architecture, their assembly language is hand-coding friendly. They adopt a straightforward load/store architecture.[71]: 4 In addition, the "interlock" mechanism, both for the data hazards and for the branch hazards, are implemented:[71]: 33–35 in other words, an assembly language programmer does not need to consider any delay slots. 32 general-purpose registers provide flexibility for assembly language users. A mixture of hand-assembled codes and C language compiled codes is facilitated by using compiler options, such as "-mno-app-regs" in the Gnu Compiler Collection.[74]

The IN instruction of the V810, which enables unsigned-load from memory-mapped I/O, was removed from the first V850s.[71]: 22 [72]: 63

Detailed discussions are available in some old journals.[75][76]

Instruction set extensions

[edit]The V850 series added many instruction set extensions, but all the extensions have backward compatibility.[77] Therefore, old binary software assets work on the new cores.

The first generation of the V850 does not have unsigned load instructions, which had been removed from the V810 (where it was implemented with IN.H and IN.B). Then, in the second generation V850E (V850E1) Series, such unsigned functionality was again added (with LD.HU and LD.BU). In addition, the V850E has some other user-friendly "CISCy" extensions, such as call table, switch, and prepare/dispose.[78]: 217

In 1996, the V853 was announced as the first 32-bit RISC microcontroller with integrated flash memory.[79] But its maximum number of "erase and write" cycles was 16.[80]: 37

In 1998, NEC strategically started to expand the V850 product line, to standard, application-specific_standard_product (ASSP), application-specific integrated circuit (ASIC), and system on a chip (SoC) businesses.[81]

In 2001, NEC launched V850ES core, which is an ultra-low-power series, but is ISA-compatible with the V850E.[82]

Around 2001, Java Acceleration IP core for the V850 seemed to be provided to some customers as SoC,[83] but detailed information is only found in some patents.[84][85]

In 2005, NEC Electronics introduced V850E2 core as the V850E2/ME3 product line with super-scalar architecture.[86]

In 2009, NEC Electronics introduced V850E2M as dual-core with 2.56MIPS/MHz and 1.5 mW/MIPS.[87]

In 2011, Renesas disclosed the SIMD extension for the V850 as V850E2H.[77][88] As for the SIMD extension, some academic studies were done.[89] But architectural documentation for this latest product line is disclosed to automotive customers only; it cannot be found on Renesas' website.[90] Its name seems to have been changed to V850E3 or G3H. The only way to know about its instruction set is to reverse engineer it with the GNU Compiler Collection.

Power consumption

[edit]The original V810 and V850 CPU architecture is designed for ultra-low power applications.

The V810 is described in detail in some journals.[91][92]

According to Renesas's documentation, the power consumption of the V850ES/Jx3-L implementation is about 70% of ARM Cortex-M3.[5]: 14, 15

The V810 was one of the most low-power 32-bit microcontroller products of the early 1990s. It operates at from 2.2 V to 5.5 V with a 5 V 0.8 μm (CZ4) fabrication process.[93] Measured with Dhrystone MIPS, power dissipation is 500 mW at 15MIPS and 40 mW at 6 MIPS, at 5 V and 2.2 V, respectively. This specification can be achieved both by well considered instruction-set architecture and by precisely tuned 5-stage 1-clock pitch pipeline microarchitecture, both of which are the benefit of a simplified RISC architecture.

This ultra-low-power architecture was succeeded by V850/Sxn product line, which are still being mass-produced after 20 years. Most of the improved chips are produced using a 3.3 V, 0.35μm (UC1) fabrication process, where the CPU core is precisely tuned to operate from 1.8 V to 3.6 V, working at 32.768 kHz (sub-oscillator) to 16.78 MHz (main-oscillator) with internal oscillator amplifier plus external resonator (crystal or ceramic).[10]

Its power dissipation is 2.7 mW/MIPS at 3.3 V when made with a 0.35 μm (UC1) fabrication process, and 3.6 mW/MIPS at 5 V with a 0.35 μm (CZ6) fabrication process. "Software STOP" stand-by mode for the mask ROM version of V850/SA1, whose internal watch timer operates at 3.3 V with 32.768 kHz sub-oscillator (IDD6), consumes typically only 8 μA electrical current. Subclock normal operation mode at 3.3 V with 32.768 kHz consumes 40 μA typically, 140 μA at the maximum. (IDD5)[94]: 440, IDD5 [13]

Its 1.8 V typical CPU operating current at 32.768 kHz might be 22 μA (40 μA ÷ 3.3 V × 1.8 V), where power dissipation should be 40 μW. It corresponds to 1.0 mW/MIPS (40 μW ÷ 0.032768 MHz ÷ 1.15 DMIPS/MHz ÷ 1000).

The V850/Sxn product line is also tuned for low noise, with both EMI and with EMS. The V850/SB1 and SB2 are especially tuned for low EMI noise with a 5 V internal voltage regulator, which facilitates high sensitivity in receiving RF for car radios.[95]: 41–44

In 2011, NEC launched the 3rd generation microarchitecture V850ES ultra-low-power series, which achieves 1.43 mW/MIPS at an operating voltage range of from 2.2 V to 2.7 V,[82] but this first implementation of V850ES microarchitecture seems to be incomplete compared with later generations of the same architecture. Its "Sub-IDLE" stand-by mode for the mask ROM version of V850ES/SA2 and V850ES/SA3, whose internal RTC operate at 2.5 V with 32.768 kHz sub-oscillator (IDD6), consume typically only 5 μA electrical current. But, Subclock normal operation mode at 2.5 V with 32.768 kHz consumes typically 40 μA, 100 μA at the maximum.[96]: 509 Its 2.2 V typical CPU operation current at 32.768 kHz might be 31 μA (40 μA ÷ 2.5 V × 2.2 V), where power dissipation should be 68 μW. This is about 1.7 times that of V850/SA1. It corresponds to 1.6 mW/MIPS (68 μW ÷ 0.032768 MHz ÷ 1.3 DMIPS/MHz ÷ 1000).

The V850ES/JG3-L product line has ultra-low-power variants, the μPD70F3792, 793, and the μPD70F3841, 842. They can operate from 2.0 V to 3.6 V with typical electrical current of 18 μA at 32.768 kHz,[97]: 1002, 1041 which should be 22 μW at 2.0 V (18 μA × 2.0 V ÷ 3.3 V × 2.0 V). This corresponds to 0.52 mW/MIPS (22 μW ÷ 0.032768 MHz ÷ 1.3 DMIPS/MHz ÷ 1000). In addition, their sub-clock idle mode power consumption, with watch timer, should be typically 3.4 μW at 1.8 V (3.5 μA ÷ 3.3 V × 1.8 V × 1.8 V).[97]: 1002, 1041

The power consumption of the NA85E2 (V850E2) core is much larger compared with the NU85E (V850E1) core using the same CB-12L (UX4L)[93][98] fabrication process. The reason is that the V850E2x core has a 128-bit instruction prefetch bus and more than one instruction prefetch queue,[99]: 16 while the average instruction length of the V800 series is 16 bits.[71]: 17 It means 16 instructions can be fetched from the memory at once, and the memory and prefetch circuits sleep fors 3 to 7 cycles for dual-pipeline superscalar architecture. This gap enlarges electrical current amplitude differences. In addition, the peak electric current exceeds allowances for the voltage stabilizers of mobile gadgets. As for V850E2M CPU core, it is publicly introduced as 1.5 mW/MIPS, 3 times that of former generations, although it should be able to take advantage of new fabrication process technologies.[87] Some mobile equipment avoids using dual-instruction execution (dual-pipeline superscalar), adopting the single-instruction (single-pipeline) execution setting to reduce electrical current amplitude differences.

Instruction opcode table

[edit]Each opcode (operation code) table is from User's Manual: Architecture (refer to external links.).

V810 (obsoleted)

[edit]- 1st map opcodes

- All opcodes (operation codes) of the hardwired control operation are contained within the first 16-bit half-word of an instruction, from the most significant bit (MSB). A 64-word depth ROM structure with branch condition code table is enough for decoding hardware. If a 16-bit literal operand is required, it is located in the second half-word. Microprogram control operations, bit strings, and floating-point arithmetic instructions are also located in the second 16-bit half-word. As a result, all the instructions have 16-bit and 32-bit 2-way form length. Unsigned load form memory mapped I/O is implemented as the

Ininstruction. Arithmetic and logical instructions are not fully, but relatively, orthogonal. - The V810 does not have saturation arithmetic instructions, but 1 additional instruction in format II, such as

SATwhich checks flags (Overflow,Sign,Zero, andHalf-word) and rewrites the specified register, might be enough both for signed and unsigned, and for word and half-word, arithmetic operations.

Bit [12:10]

[15:13, 9]000 001 010 011 100 101 110 111 Format 000 X MOV ADD SUB CMP SHL SHR JMP SAR I(R,r) 001 X MUL DIV MULU DIVU OR AND XOR NOT 010 X MOV ADD SETF CMP SHL SHR SAR II(imm5,r) 011 X TRAP RETI HALT LDSR STSR Bit str.

100 0

100 1Bcond III(disp9) BV BZ/BE BN(BS) BLT BNV BNZ/BNE BP(BNS) BGE BC/BL BNH BR BLE BNC/BNL BH NOP BGT 101 X MOVEA ADDI JR JAL ORI ANDI XORI MOVHI IV/V 110 X LD.B LD.H LD.W ST.B ST.H ST.W VI(disp16[R],r) 111 X IN.B IN.H CAXI IN.W OUT.B OUT.H Float OUT.W VI/VII

NOPis an alias ofNon-BR.

V850 (1st Gen.)

[edit]- 1st map opcodes

Bit [7:5]

[10:8]000 001 010 011 100 101 110 111 Format 000 MOV NOT DIVH JMP SATSUBR SATSUB SATADD MULH I(R,r) 001 OR XOR AND TST SUBR SUB ADD CMP 010 MOV SATADD ADD CMP SHR SAR SHL MULH II(imm5,r) 011 SLD.B SST.B IV(disp7[ep],r) 100 SLD.H SST.H IV(disp8[ep],r) 101 Bit[0] SLD.W / SST.W Bit[3:0] Bcond IV/III 110 ADDI MOVEA MOVHI SATSUBI ORI XORI ANDI MULHI VI(disp16[R],r) 111 LD.B 2nd Map ST.B 2nd Map JARL Bit[15:14]

SET1/NOT1

/CLR1/TST12nd Map

ExtensionV/VII/VIII

NOPis an alias ofMOV R0,R0.

- 2nd map opcodes

Bit [23:21]

000 001 010 011 100 101 110 111 Format [16] 1st Map Bit[10:5]=111001 0 LD.H VII 1 ST.H VII [16] 1st Map Bit[10:5]=111011 0 LD.W VII 1 ST.W VII [26:24] 1st Map Bit[10:5]=111111 000 SETF LDSR STSR undef SHR SAR SHL undef IX(R,r) 001 TRAP HALT RETI 1st Map

Bit[15:13]

EI/DI

undefIllegal instruction X 01X Illegal instruction — 1XX Illegal instruction —

V850E/E1/ES

[edit]- 1st map opcodes

Bit [7:5]

[10:8]000 001 010 011 100 101 110 111 Format 000 —† NOT SWITCH JMP ZXB SXB ZXH SXH I(R,r0) MOV DBTRAP Bit[4]

SLD.BU

/SLD.HUSATSUBR SATSUB SATADD MULH I(R0,r31) / IV undef I(R0,r) / IV DIVH I(R,r) / IV 001 OR XOR AND TST SUBR SUB ADD CMP I(R,r) 010 CALLT ADD CMP SHR SAR SHL undef II(imm5,r0) MOV SATADD MULH II(imm5,r) 011 SLD.B SST.B IV(disp7[ep],r) 100 SLD.H SST.H IV(disp8[ep],r) 101 Bit[0] SLD.W / SST.W Bit[3:0] Bcond IV/III(disp9) 110 ADDI Bit[15:11]

MOV(r=0)Bit[15:11]

DISPOSE(r=0)ORI XORI ANDI Bit[15:11]

undefVI(imm16,R,r)

/VI(imm32,R)

/XIIIMOVEA MOVHI STASUBI MULHI 111 LD.B 2nd Map ST.B 2nd Map Bit[15:14]

SET1/NOT1

/CLR1/TST12nd Map VII(disp16[R],r)

/VIII(imm3,disp16[R])

- †

NOPis an alias ofMOV R0,R0.

- 2nd map opcodes

Bit [23:21]

[16, 26:24]000 001 010 011 100 101 110 111 Format 1st Map Bit[10:5]=111001 0 XXX LD.H VII(disp16[R],r) 1 XXX ST.H 1st Map Bit[10:5]=111011 0 XXX LD.W VII(disp16[R],r) 1 XXX ST.W 1st Map Bit[10:5]=11110X 0 XXX 1st Map Bit[15:11] JR(r=0) / JARL (r≠0) V(disp22) 1 XXX 1st Map Bit[15:11] PREPARE(r=0) / LD.BU XIII/VII(disp16[R],r) 1st Map Bit[10:5]=111111 0 000 SETF LDSR STSR undef SHR SAR SHL Bit[18:17]

SET1/NOT1

CLR1/TST1IX(R,r)

IX(R,[r])0 001 TRAP HALT Bit[18:17]

RETI/CTRET

/DBRET

/undef1st Map

Bit[15:11]

EI/DI

undefundef X 0 010 SASF Bit[17]

MUL(R,r,w)

/MULU(R,r,w)Bit[17]

MUL(imm9,r,w)

/MULU(imm9,r,w)Bit[17]

DIVH(R,r,w)

/DIVHU(R,r,W)Bit[17]

DIV(R,r,w)

/DIVU(R,r,w)IX(R,r)

/XI(R,r,w)

/XII(imm9,r,w)0 011 CMOV(imm5,r,w) CMOV(R,r,w) Bit[18:17]

BSW/BSH

HSW/undefundef Illegal instruction XI(c,R,r,w)

/XII(c,imm5,r,w)0 10X Illegal instruction 1 XXX LD.HU VII(disp16[R],r)

List of the V800 Series CPU cores

[edit]| CPU core | Product variants | GCC targeting options[100] | Remarks |

|---|---|---|---|

| V810[1] (1991) |

V810 family (V810, V805 V820, V821[101]) |

Revert patch required.[53] Available on Planet Virtual Boy. GCC named gccVB. |

Obsoleted products. Unsigned & signed load. μcoded float (single)[102] 1 KB I-cache. 5-stage pipeline.[103] 6.7 mW/MIPS (5 V Product) |

| V830[104] (1997) |

V830 family (V830 — V833[54][104][105]) |

ditto | Obsoleted products. High end products. Multimedia extension. 16 KB on-chip memory. Multiply accumulate. Saturation arithmetic Branch prediction.[106] |

| V850 (1994) |

V850 family started V851 — V852[107] V853,[79][108][109] V854 |

none or -mv850 | Obsoleted products. 5-stage pipeline. 4.4 mW/MIPS (5 V product) |

| V850 (1997) |

V850/xxn (e.g. V850/SA1) |

none or -mv850 | Not for new developments. Signed load. 1.15 Dhrystone MIPS/MHz Ultra-low power products. 3.6 mW/MIPS (5 V product) 2.7 mW/MIPS (3.3V product) 1.0 mW/MIPS (1.8 V Sub-ope.) |

| V850E (1996) |

V850E/MS1,[110][111] V850E/MS2 |

-mv850e | Not for new developments. Unsigned & signed load. 1.3 Dhrystone MIPS/MHz Standard products. |

| V850E1 (1999) |

V850E/xxn (e.g. V850E/MA1[22]) NB85E SoC core[112][113] NU85E SoC core[112][113] (Sony's & NEC's best-cellular.) |

-mv850e1 or ‑mv850es | Unsigned & signed load. N-Wire and N-Trace. Standard products. SoC Products. |

| V850ES (2002) |

V850ES/xxn(-x) (e.g. V850ES/SA2) |

-mv850es or ‑mv850e1 | Unsigned & signed load. Ultra-low power products. 1.43 mW/MIPS (2.5 V product) 0.52 mW/MIPS (2.0 V Sub-ope.) Shift to V850E2S requested. |

| V850E1F (2005) |

V850E/PH2, V850E/PH3 V850E/PHO3 |

Patch required (maybe). | H/W float (single precision). |

| V850E2 (2004) |

V850E2/ME3 NA85E2 SoC core[112][114] (NEC's long-running cellular. Sets life = 2004–2012.) |

-mv850e2 | Not for new developments. Many errata but still alive. Single insn. executing. (Dual-executing errata.) 7-stage pipeline. S/W float. Standard Products. SoC Products. |

| V850E2(v2) () |

V850E2/xxn (e.g. FIX ME) NB85E2 SoC core[112][114][115] |

-mv850e2 | Errata cleaned up. Dual instruction executing. 7-stage pipeline. S/W float. Standard Products. SoC Products. |

| V850E2M (2009) G3 |

V850E2/xxn (e.g. V850E2/FG4) RH850/nxn |

-mv850e2v3 and -msoft-float | S/W float. Dual instruction executing. 7-stage pipeline. 2.56 Dhrystone MIPS/MHz 1.5 mW/MIPS Multi CPU core support. Memory Protection. |

| V850E2R (2010) G3R |

V850E2/xxn (e.g. V850E2/MN4) RH850/nxn |

-mv850e2v3 | H/W float (double precision). Dual instruction executing. 7-stage pipeline. 2.56 Dhrystone MIPS/MHz Multi CPU core support. Memory Protection. |

| V850E2S (2011) G3K |

V850E2/xxn(-x) (e.g. V850E2/Jx4-L) (e.g. V850E2/Fx4-L) RH850xnx |

-mv850e2v3 and ‑msoft‑float | S/W float. 5-stage pipeline. 1.9 Dhrystone MIPS/MHz Multi CPU core support. Memory Protection. Ultra-ultra-low power. Standard products. V850ES/xxn pin compat. Automotive products. Shift to RH850 requested. |

| V850E2H (2010)[116] V850E3 (2014) G3M G3MH, G3KH |

RH850/xnx (e.g. RH850/C1H) |

-mv850e2v4 and ‑mloop or -mv850e3v5 and ‑mloop |

SIMD extension. 64-bit multiple load/store. Loop extension. H/W float (double precision). Memory Protection. Multi CPU core support. Automotive products. |

[101][105][110][111][1][103][53][107][108][109][112][116]

SoC solutions

[edit]SoC IP cores

[edit]In 1998, NEC started to provide the V850 family as an ASIC core, to expand its ASIC business.[117]

In addition, both the V850E1 CPU core named Nx85E[118][119]

and the V850E2 CPU core named Nx85E2,[120]

are also used for expanding its ASIC products business.

Various SoCs utilize this core. In 2003, for example, Dotcast, Inc. used the NU85E core for a set top box receiver of digital datacasting based on the dNTSC (data in NTSC video method[121]). This core is fabricated with CB-10 0.25μm 5-layered-metal process technology.[122]: 9–10

The NA85E2C core, which is developed using a 1.5 V 150 nm CB-12L (UX4L) fabrication process,[93][98] has many errata (4 pages appendix in preliminary architecture manual,[123]: 230–233 plus a further, 7-page restrictions document[124]), but which doesn't seem to matter, because this is a product with a long lifespan.

NEC also expanded production of a core using a 130 nm CB-130 (UX5) fabrication process,[93] cell-base IC.[125][126]

Synopsys DesignWare IP core for V850E was once announced,[127] but support has been discontinued.[128]

| Name | Core | Cell-base series |

Power supply |

Node/ Gate L |

Fab. proc. [93] |

Freq. MHz |

Type | ICE | Docs. |

|---|---|---|---|---|---|---|---|---|---|

| NA851C | V851 | CB-9VX | 3.3 V | 350 nm | UC1 | 33 | With peripheral | [117][129] | |

| NA853C | V853 | CB-9VX | 3.3 V | 350 nm | UC1 | 33 | With peripheral | [117][130] | |

| NA85E | V850E1 | CB-9VX | 3.3 V | 350 nm | UC1 | Bulk core | [118] | ||

| NB85E | V850E1 | CB-9VX | 3.3 V | 350 nm | UC1 | 66 | Bulk core | [131][132] | [117][119][133] |

| NB85ET | V850E1 | CB-9VX | 3.3 V | 350 nm | UC1 | 66 | w/ Trace I/F | [131][132] | [117][133] |

| NB85E | V850E1 | CB-10 | 2.5 V | 250 nm | UC2 | 66 | Bulk core | [131][132] | [133] |

| NB85ET | V850E1 | CB-10 | 2.5 V | 250 nm | UC2 | 66 | w/ Trace I/F | [131][132] | [133] |

| NU85EA | V850E1 | CB-10VX | 2.5 V | 250 nm | UC2 | 100 | Bulk core | [131][132] | [133][134][135][136] |

| NU85ET | V850E1 | CB-10VX | 2.5 V | 250 nm | UC2 | 100 | w/ Trace I/F | [131][132] | [133][134][135][136] |

| NDU85ETV14 | V850E1 | CB-12L | 1.5 V | 150 nm/ 130 nm |

UX4L | w/ Trace I/F | [131][132] | [133][134][135] | |

| NDU85ETVxx | V850E1 | CB-12M | 1.5 V | 150 nm/ 130 nm |

UX4M | w/ Trace I/F | [131][132] | [133][134][136] | |

| NA85E2C | V850E2 | CB-12L | 1.5 V | 150 nm/ 130 nm |

UX4L | 200 | w/ Trace I/F | [114][137] | [133][136] |

| NB85E2C | V850E2 | CB-12L | 1.5 V | 150 nm/ 130 nm |

UX4L | 200 | w/ Trace I/F | [114][137] | [133][136] |

| V850E2x | CB-130L | 1.2 V | 130 nm/ 95 nm |

UX5L | |||||

| — | — | CB-90L | 1.2 V | 90 nm/ |

UX6L | Replaced by ARM946.[115] | |||

| In-house | V850E2x | UX6LF | 1.2 V | 90 nm/ |

UX6LF | Renesas internal use only ??? | |||

| — | — | CB-65L | 1.2 V | 65 nm/ |

UX7L | Skipped. Replaced by ARM1156.[115] | |||

| — | — | CB-55L | 1.2 V | 55 nm/ 50 nm |

UX7LS | Skipped. Replaced by ARM Cortex-M3. | |||

| — | — | CB-40L | 1.1 V | 40 nm/ 40 nm |

UX8L | Replaced by ARM Cortex-M4. | |||

| In-house | V850E3 | RV40F | 1.1 V | 40 nm/ 40 nm |

RV40F | 320 | Renesas internal use only ??? |

FPGA prototyping systems for SoC

[edit]FPGA prototyping systems for V850E1, V850E2, and V850E2M core-based SoCs were intensively developed to expand the SoC business. They comprised a V850 CPU core LSI (TEG, or Test Element Group) board and FPGA add-ons. Most SoC products were for mobile equipments, because the power dissipation of original V800-Series RISC architecture was much lower compared with CISC.[1][5][103] It is similar to the ARM architecture that is widely used for mobile gadgets.

- Renesas (NEC): Microssp (2006)[115]

- Renesas (NEC): Hybrid Emulator (2007)[142]

- Renesas (NEC): PFESiP EP1 Evaluation Board (2008)[143]

- Renesas (NEC): PFESiP EP1 Evaluation Board Lite (2008)[144]

- Renesas (NEC): PFESiP EP3 Evaluation Board (2010): V850E2M CPU core, max. 266 MHz operation[145]

Strategic confusion

[edit]Around 2011–2014, Renesas Electronics extensively expanded the V850E2 product line,[148][149] but this high-paced expansion brought much confusion. For example, as of 2018, some have requested that V850E2/xxn products be replaced with RH850/xnx ones.[150]

In addition, in 2012 Renesas started to intensively promote the migration from ten-year-old V850ES/Jx3 product lines to the newly produced V850E2/Jx4, such as for Ethernet and USB applications,[151][152] but the newer products are not listed on their website, as of 2018.[39]

Currently,[as of?] Renesas Electronics is designing a "dual" "lockstep" system, but its predecessor NEC V60-V80 had "multiple modular" lockstep mechanism called FRM,[153] either with roll-back by "retry" or with roll-forward by "exception" for each fault detected instruction.

In addition, the NEC V60-V80 has several implementations of UNIX System V port product releases, one of which is "real-time UNIX RX/UX-832"[154] (here, 832 stands for the μPD70832 (V80), not V832). Its multiprocessor implementation is called MUSTARD (Multiprocessor Unix for Embedded Real-Time Systems), which can operate a maximum of 8 processors simultaneously, and its lockstep mechanism was dynamically configurable.[155]

In 2001, both NEC Corporation and Synopsys, Inc., announced they had agreed to promote the V850E as DesignWare IP core.[127][128] But as of 2018, the V850E is not listed on DesignWare libraries.[156]

Lucent Technologies and Texas Instruments once licensed the V850 and V850E SoC cores, respectively,[157][158][159][160] but those devices cannot be found.

In 2006,Metrowerks developed the CodeWarrior compiler for the V850, which was one of the main compilers for the V850,[161] but around 2010, they discontinued support.

Also in 2006, NEC did not give any roadmap for the V850 family as SoC cores.[115] The V850E2 core, developed in 2004, was described as the last, best core for SoC applications. However, NEC introduced ARM9 (arm v5) and ARM11 (arm v6), especially for mobile equipment. This decision suddenly decreased the net profit of LSI devices, because of the royalty for using ARM, and thus price competition with other ARM SoC providers. The sales revenue of "V850 total solutions", such as development tools, real-time OS, middle-ware packages, and in-circuit emulators, also decreased. The number of V850 devices sold also suddenly decreased, because mobile equipment manufacturer were the major customers of V850E1 and V850E2 cores at that moment.[162]

In 2008, KMC (Kyoto Mictocomputer), which is one of the major and of the first providers of in-circuit emulators for the V850 family, announced "exeGCC" being updated from Rel. 3 to Rel. 4,[163] but it excluded the V850 from this updating list, which added PowerPC and ARM v7. KMC chose SH-4A and ARM v7, instead of V850 and RH850,[164] though it had been working closely with NEC and Renesas Electronics.[161]

The V850 CPU cores run uClinux,[165] but on October 9, 2008, Linux kernel support for the V850 was removed in revision 2.6.27.,[166] because NEC stopped its maintenance.[167][168][169] The person in charge of V850 Linux kernel maintenance was moved from NEC to Renesas by its merger, but his new job was compiler design and never returned to Linux kernel maintenance.[170] This corporate decision prevented the possibility of porting to Android.[171] As of 2018, Renesas Electronics mainly focuses Linux kernel support on SH3/SH4 and M32R processors. [172][173][174][175][176]

Target software solutions

[edit]Libraries

[edit]- Red Hat, Inc.: The Newlib for C runtime library (libc.a) and mathematical library (libm.a)[177]

- C runtime startup routine (crt0.S) for the latest v850e3v5 microarchitecture is available.[178][179][180]

- Micro Digital Inc.: GoFast for NEC V85x Fast Software Floating Point Library[181]

- The GNU Compiler Collection: Software floating point[182]

- The GNU Compiler Collection: Decimal floating point (libdecnumber.a)[183]

Operating systems

[edit]V850 Operating systems are mostly real-time.

Some operating systems require a memory protection unit (MPU) to divide tasks (or threads) strictly for reliability and safety reasons. In such cases, the v850e2v3 (Gen. 3) microarchitecture, or above, is required.

ITRON based real-time OS

[edit]ITRON is an open standard specification of real-time OS (RTOS), which is major in Japan. Its specification is defined under the leadership of Ken Sakamura, as a part of TRON project, the initialr I standing for "Industrial". Because the ITRON specification defines interface and skeleton only, each vendor has its own implementation.

- Renesas:

- Toppers Project: Open source TOPPERS/JSP

- A.I. Corporation: Toppers-Pro/xxx[189]

- T-Engine Project: Open source T-Kernel by TRON Forum[190]

- eSOL: eT-Kernel; Extended T-Kernel — RTOS for embedded systems[191][192]

- eT-Kernel/Compact, eT-Kernel/Embedded, eT-Kernel/POSIX

- eT-Kernel Multi-Core Edition

- eCos: Open source real-time operating system

AUTOSAR, OSEK/VDX compliant real-time OS

[edit]AUTOSAR is an open systems architecture of operating system for the automotive industry. Its purpose is to standardize electronic control units (ECU) for automotive engines. AUTOSAR is an upward compatible specification of OSEK/VDX, which is also a German consortium established in 1993.

In Japan, this research was started in 2006, as a joint project by JAIST and DENSO. Renesas Electronics joined this project in 2009.[193] Because the current RH850 and V850 processors are principally targeted at the automotive industry, it is a strategical product of Renesas Electronics. However, its documentation is only available in Japanese, as its main customer is Toyota Motor Corporation.

- Renesas: RV850 (documents are in Japanese only)[194]

- ETAS GmbH: RTA-OS RH850/GHS,[195] RTA-OSEK V850E/GHS[196]

- Mentor Graphics (formerly Accelerated Technology, Inc.): Nucleus OSEK[197]

- HighTec EDV-Systeme GmbH: EB tresos Safety OS[198]

- Toppers Project: Open source TOPPERS/AUTOSAR[199]

- eSOL: eMCOS AUTOSAR profile[200]

Other real-time OS

[edit]- eSOL:

- eMCOS; Scalable RTOS, Distributed Microkernel Architecture, non-hypervisor type OS[205]

- MiSPO:

- NORTi Professional; Real-time OS + TCP/IP stack + Simulator[206]

- Mentor Graphics (formerly ATI, currently A Siemens Business):

Linux

[edit]- On October 9th 2008, Linux kernel support for V850 was removed in revision 2.6.27,[166] preventing the possibility of porting Android.[171]

Middleware packages

[edit]Various middleware application softwares are provided from various vendors.

- Renesas: SD Memory Card Control[214]

Software development tools

[edit]Compilers and assemblers

[edit]Most of the compilers, for both for the V850 family and the RH850 family, are exactly the same product, and extended ISA targets are controlled by command line options.[215][216]

Compilers for the V850 family and the RH850 family include:

- The GNU Compiler Collection (the name is still v850 for RH850)[217] developed both:

- by "Red Hat, Inc." (formerly "Cygnus Solutions") as a part of the GNUPro Developers Kit[218]

- by "KMC (Kyoto Micro Computer)" as a part of the exeGCC[161][219][220]

- by "CyberTHOR Studios, Ltd.": Free pre-built binaries can be downloaded by registration.[221]

- Renesas:

- C Compiler Package for V850 family[222]

- CA850 C compiler for V850E1 and V850ES (v850e1 and/or v850es, a.k.a. Gen. 1)[223]

- CX C compiler for V850E2M and V850E2S (v850e2v3, a.k.a. Gen. 3)

- Software Package for V850 [SP850] for V850E2 (v850e2(v2), a.k.a. Gen. 2)[224]

- CC-RH C compiler package for G3, G3K(H), G3M(H)[225]

- C Compiler Package for V850 family[222]

- GHS (Green Hills Software): The Green Hills Optimizing Compilers[226][227]

- Wind River Systems: Diab Compiler[228][229]

- IAR Systems: Embedded Workbench[230]

- Altium Limited: Tasking; RENESAS RH850 SOFTWARE DEVELOPMENT TOOLS[231]

- Metrowerks: CodeWarrior (obsoleted)[161]

Disassemblers

[edit]Usually, dis-assemblers are provided as a part of C compiler or assembler packages.

- The GNU Binutils: objdump (v850-elf-objdump or v850-elf32-objdump)[236]

- Radare2: Radare2 is a set of command-line tools for reverse engineering.[237] Open-source code is available from GitHub repository.[238][239]

- IDA Pro: IDA Pro is a freeware disassembler for hobby use. A plugin for V850 is available. Download site is gray for securities.[240]

GUI based debuggers

[edit]GUI based program debuggers are mainly provided for debugging of compiled source codes. Usually, it is used with instruction set simulators or in-circuit emulators.

- Renesas:

- ID850: For the combination of CA850 compiler and SM850 instruction set simulator.

- ID850NW: For the combination of N-Wire based in-circuit emulators.

- ID850QB: For the combination of probing-pod based emulator IEQUBE2

- NDK (Naito Densei Kogyo Co. Ltd, Group): Operation started in 1950 as subsidiary of NEC.

- NW-V850-32

- GHS (Green Hills Software): Multi: General-purpose debugger.

- Red Hat, Inc.: Insight (GDB-Tk): GUI front-end tightly combined with GNU Debugger.

- Mentor Graphics (formerly Accelerated Technology, Inc.): code|lab Developer Suite[241]

- By N-Wire based in-circuit emulator vendors:

Instruction set simulators

[edit]Instruction set simulator, in other words, Virtual Platform is provided to perform debugging without equipment's hardware before testing on a real machine.

- Renesas: SM850[244]

- Open Virtual Platform: Instruction set simulator[245]

- Synopsys: VDK for Renesas RH850 MCU[246]

Automated code reviewers

[edit]Automated code reviewer, in other words, source code analyzer qualify the level of completeness of written software source code. This method is classified as dynamic code analysis and static code analysis.

Dynamic code analyzers with simulators

[edit]- Renesas: TW850

- TW850 Performance Analysis Tuning Tool is a general utility to improve effectiveness of software.[247]

- Renesas: AZ850

- AZ850 System Performance Analyzer is a utility for RX850 real-time operating system to evaluate effectiveness of application programs.[248]

- Gaio Technology: Coverage Master winAMS[249]

- Coverage Master winAMS is a source code coverage measurement tool.

Static code analyzers

[edit]- GHS (Green Hills Software): DoubleCheck ISA (Integrated Static Analysis) tool[250]

- Rogue Wave Software, Inc: Klocwork[251]

IDE (Integrated Development Environments)

[edit]IDE, Integrated Development Environment, is a framework to provide software development functions.

- Renesas: CS+ (formerly CubeSuite+)[252]

- GHS (Green Hills Software): Multi

- Eclipse Plugins

- GNU Compiler Collection (GCC) and GNU Debugger (GDB)

- Wind River Workbench (formerly Tornado)

Hardware development tools

[edit]ICE (In-circuit emulators)

[edit]Most in-circuit emulators, such as Renesas's IE850 (formerly IECUBE2),[253] can be used for both the V850 family and the RH850 family, but may require firmware updating. The latest "trace function" of the JTAG (N-Wire[254]) based in-circuit emulator is upgraded from the N-Trace (single-ended signaling)[255] to the Aurora Trace (differential signaling).[256]

Full probing pod type

[edit]Full probing pod type in-circuit emulator is sometimes called full ICE or legacy ICE.

- Renesas IE850 (formerly IECUBE2)[253]

- Naito Densei Machida Mfg. Co., Ltd. (Operation started as NEC's subsidiary.)

- Asmis brand for custom LSIs.[257]

ROM emulator type

[edit]- Lauterbach: ROM Monitor for V850[258]: 5

- KMC (Kyoto Microcomputer Co., Ltd.): PARTNER-ET II (obsoleted)[259]

JTAG N-Wire and N-Trace type

[edit]N-Wire and N-Trace[260][255][261][262] is a JTAG-based debugging interface specification, which circuit implementation is called TAP Controller (Test Access Port controller),[263] primarily compiled by Philips N.V. (currently NXP Semiconductors). But it is perhaps not disclosed publicly in its earlier stage. As the result, each semiconductor and in-circuit emulator vendor implemented similar interfaces independently. Nowadays, it is standardized by IEEE 1149.1 Working Group.[264]

- Renesas

- Naito Densei Machida Mfg. Co., Ltd. (Operation started as NEC's subsidiary.): Asmis brand.[267]

- Midas Lab.: RTE-2000H[268] with PARTNER[131][242] debugger

- Lauterbach: Trace32[258][269][270]

- iSystem: BlueBox iC5000 and iC5700[271][272]

- IAR Systems

- DTS INSIGHT (formerly YDC; Yokogawa Digital Computer): adviceLUNA II[273][274]

- Computex: PALMiCE3 V850[275]

- Sohwa & Sophia Technologies: Universal Probe Blue[276] with WATCHPOINT debugger[243]

- KMC (Kyoto Microcomputer Co., Ltd.): PARTNER-Jet (obsoleted)[277]

Nexus and Aurora trace type

[edit]Nexus or IEEE-ISTO 5001-2003 is a standard debugging interface for embedded systems.

Aurora is a high speed signal transfer specification. Its data link layer communications protocol is a point-to-point serial links, and physical layer is a high speed differential signaling.

- Lauterbach: Trace32: PowerTrace for NEXUS[278]

- iSystem: BlueBox iC5000 and iC5700 (Nexus), iC6000 (Aurora)[271][279]

Flash ROM programmers

[edit]Because the V850 family is developed as a single chip microcontroller, every product integrates non-volatile memory. In its first stage, it was one-time programmable or UV EPROM type, but in V853, V850/xxn Series, and later, it becomes flash memory type.

Gang writers (gang programmers)

[edit]A gang writer, or a gang programmer, is an old terminology for programmable ROM writers, or programmers. Its name comes from that it steals the binary code from one device, and write it to several others simultaneously. This read device is sometimes called a master device. For mass production use, a dedicated attachment board with "a set of sockets", i.e. "a gang", is needed. As usual, instead of a programmed master device, an object code file can be copied from a PC via download cable, or from a USB stick. Most gang writers accept ASCII-format files such as Intel HEX and Motorola SREC, or binary format files such as ELF.

This method is suitable for mass production.

- TESSERA Technology Inc.: Stick GANG Writer[280]

Programming service providers

[edit]Flash ROM programming service providers exist in most countries.

- Minato Holdings, Inc.

- Minato Holdings, Inc. (in Japanese)[281] is a Japanese company that started as an automated test equipment vendor for memory LSIs. Nowadays, it provides flash ROM programming services for various devices, including V850 and RH850, with its own gang writers and full automatic device handler machines.

On board programming with ICE

[edit]Most JTAG-based in-circuit emulators have an on board flash ROM programming function via a debug port,

which may be according to IEEE standard 1532-2002, a standard for in-system configuration of programmable components.[282]

Direct connection via RS-232C

[edit]If the target board has a RS-232C connector and a transceiver (driver/receiver) IC, such as ICL32xx,[283] for the UARTx peripheral function of V850 device, flash ROM programming with a directly connected PC might be available (depends on devices[284]: 16–24 ). The Renesas Flash Programmer software V2[285] or V3[286] is required.

Dedicated on board programmer

[edit]On-board programming is also available via UARTx or CSIx+HS peripherals on V850 devices by using dedicated programmer hardware (depends on devices[284]: 16–24 ).

- Renesas: PG-FP6[287]

Ancient PROM writers

[edit]To program V851[288]: 11, 14–20 and V852,[289]: 11, 14–20 an ancient PROM programmer with dedicated adapter is required.

- Renesas PG-1500 (obsoleted)

- Renesas PG-1500[290] is a programmable ROM writer compatible with 27C1001A[291] devices, UV EPROM, or one-time PROM (OTP). This writer reads a silicon signature[292][293] from each device before programming, by asserting 12.5 V to the A9 (address #9) terminal. It must NOT be used for modern flash ROM burning.

Gray zone tools

[edit]Some gray zone hacking tools exist for V850 on car dashboards.

- VVDI PROG.:

- OBDexpress[294]

Evaluation boards

[edit]See also

[edit]References and notes

[edit]- ^ a b c d

Harigai, Hisao; Kusuda, Masaori; Kojima, Shingo; Moriyama, Masatoshi; Ienaga, Takashi; Yano, Yoichi (1992-10-22). "低消費電力・低電圧動作の32ビットマイクロプロセッサV810" [A low power consumption and low voltage operation 32-bit RISC Microprocessor] (PDF). SIG Technical Reports, Information Processing Society of Japan. 1992 (82 (1992-ARC-096)): 41–48.

Abstract:

An advanced 32-bit RISC microprocessor for embedded control; V810 is introduced in this paper. The V810 has high performance and application specified functions. V810 dissipates less power than any other RISC chips. The V810 is the first 32-bit RISC microprocessor that operates at 2.2 V.

The V810 chip is fabricated by using 0.8 μm CMOS double metal layer process technology to integrate 240,000 transistors on a 7.7×7.7 mm2 die. - ^ "NEC : Shareholder Information". www.nec.com.

- ^ a b NEC (April 1999). "SEMICONDUCTORS SELECTION GUIDE" (PDF) (17th ed.). Archived from the original (PDF) on 2018-01-08.

- ^ "CA830, CA850 C COMPILER PACKAGES" (PDF). NEC.

- ^ a b c Wang, Bobby (2010-08-04). "V850 Architecture Overview, High performance and Energy Efficient" (PDF). Renesas Electronics Corporation.

- ^ "NEC ND-3530A firmware update like ND-3520A or ND-3540A". Club Myce – Knowledge is Power. 4 September 2010. Archived from the original on 14 May 2019. Retrieved 25 September 2022.

- ^

"Optiarc AD7240S". www.cdrinfo.com. Team CDRInfo.COM. 2009-06-29.

Built-in CPU functionality

• Onboard 32-bit RISC CPU (V850ES core)

• Built-in RAM (14KB)

• Power management functionality

• Built-in peripheral circuits (timer, interrupt controller, serial interface) - ^ MOTOYAMA, Yoshiak; SATO, Noboru; HONMA, Hiromi; JIMI, Junich; SHIBATA, Iwao (2006-12-25). "SCOMBO/UM: World's First Optical Drive System LSI to Support Recording/ Playback of Both Next-Generation DVD Formats, HD DVD and BD" (PDF). Nec Technical Journal. 1 (5). NEC: 15–18. ISSN 1880-5884. 200902288400231201.

- ^ "First LSI to Offer Blu-Ray and HD DVD Writing". www.cdrinfo.com. Team CDRInfo.COM. 2006-10-10.

- ^ a b c "NEC to Market Ultra-Low Power Consumption, Low-Noise 32-bit RISC Single-Chip Microcontroller Ideal for Portable Equipment". NEC (Press release). 1997-08-28.

- ^ "32-BIT RISC MICROCONTROLLER V850/SV1" (PDF). NEC Device Technology International. 1999 (54). NEC.

- ^ V850/SA1 for Hardware (PDF) (4.01 ed.). Renesas. 2005-08-01.

- ^ a b "V850/SA1". Renesas Electronics.

- ^ Suto, Shinichi. "32-BIT RISC MICROCONTROLLER V850/SBx" (PDF). NEC Device Technology International. 1998 (51). NEC.

- ^ "NEC 32-bit RISC Single-chip Microcomputer Features High Performance, Ultra-Low Power Consumption, Low Noise and Peripheral Functions". www.nec.co.jp. 1998-08-24.

- ^ "V850/SC1, V850/SC2". Renesas Electronics.

- ^ "NEC Unveils Family of 32-bit RISC Microcontrollers with Optimal Performance/Power Ratios for Consumer, Industrial and Automotive Applications V850/SCx Family MCUs offers large memory options, pin-for-pin compatibility with existing controllers and numerous peripherals". NEC (Press release). 2001-04-01.

- ^ Naito, Yukihiro; Hikishima, Naoki; Ohta, Yoshiaki; Hatabu, Atsushi; Kuroda, Ichiro (20 April 2001). "W-CDMA端末用ビデオフォン" [Video-Phone for W-CDMA Terminal] (PDF). The Journal of the Institute of Image Information and Television Engineers (in Japanese). 55 (4): 497–498. doi:10.3169/itej.55.497. ISSN 1881-6908.

- ^ F35-XXL Hardware description (PDF) (1.10 ed.). FALCOM GmbH. 2014-06-24.

- ^ Eltze, Jens (1997). "Double-CAN Controller as Bridge for Different CAN Networks" (PDF). 4 Th International CAN Conference. CAN in Automation (CiA) international.

- ^ Ishikawa, Tatsuya. "32-BIT RISC MICROCONTROLLER V850/SF1" (PDF). NEC Device Technology International. 2000 (57). NEC.

- ^ a b Kubota, Kei. "32-BIT RISC SINGLE-CHIP MICROCONTROLLER V850E/MA1" (PDF). NEC Device Technology International. 1999 (54). NEC.

- ^ "V850E/ME2". Renesas Electronics.

- ^ Ohbuchi, E.; Hanaizumi, H.; Lim Ah Hock (2004). "Barcode Readers using the Camera Device in Mobile Phones". 2004 International Conference on Cyberworlds. pp. 260–265. CiteSeerX 10.1.1.335.8157. doi:10.1109/CW.2004.23. ISBN 0-7695-2140-1. S2CID 15634963.

- ^ Yun Chan Cho; Jae Wook Jeon (2007). "Current software platforms on mobile phone". 2007 International Conference on Control, Automation and Systems. pp. 1862–1867. doi:10.1109/ICCAS.2007.4406649. S2CID 16120691.

- ^ Kaneko, Yasunori; Fumio, Suto; Umeda, Koji; Shiraishi, Mitsutaka; Shirota, HIrobumi; Suka, Takeya (2002-04-25). "デジタル・ムーバN503iS HYPERの開発" [Development of Digital Mova N503iS HYPER.]. NEC Technical Journal (in Japanese). 55 (4): 156–159. ISSN 0285-4139.

- ^ Kayama, Naoyuki; Mizoguchi, Tamiyuki; Ehara, Tatsuji; Osawa, Takeshi; Umezawa, Atsushi; Yamada, Yasuyoshi (2003-03-10). "ムーバN504iSの開発" [Development of Mova N504iS.]. NEC Technical Journal (in Japanese). 56 (2): 52–55. ISSN 0285-4139.

- ^ Yamashita, Masayoshi; Takenaka, Hidetoshi; Inoue, Jiro; Terada, Shigehiro; Yamada, Hironori; Akiyama, Makoto (2003-09-25). "ムーバN505iの開発" [Development of mova N505i]. NEC Technical Journal (in Japanese). 56 (8). NEC: 33–37. ISSN 0285-4139. 200902227791143957.

- ^ Torihata, Toshiaki. "32-BIT RISC SINGLE-CHIP MICROCONTROLLER V850E/IA1" (PDF). NEC Device Technology International. 1999 (55). NEC.

- ^ Torihata, Toshiaki (2001). "32-BIT RISC SINGLE-CHIP MICROCONTROLLER V850E/IA2" (PDF). NEC Device Technology International. 2001 (61). NEC. S2CID 51805607. Archived from the original (PDF) on 2018-02-25.

- ^ "NEC Adds Inverter Control Functions in 32-bit Single-chip RISC Microcontroller". NEC (Press release). 1999-08-24.

- ^ "V850E/IA3, V850E/IA4". Renesas Electronics.

- ^

Nonaka, Yoshiya; Denda, Akihiro; Uesaka, Gakuji; Sakamoto, Yuji; Nii, Noritaka; Satou, Masahiro; Endo, Kazuaki; Katou, Hiroki; Sugino, Ryouji; Sada, Takeshi; Endo, Koji; Nishigata, Junko; Ishiyama, Kunihiro; Morita, Kenji (2002). "HDD-DEH のソフトウェア開発" [Software Development of CD/MP3/Memory Stick Player with HDD] (PDF). Pioneer R&D (in Japanese). 12 (3). Pioneer Corporation: 26–38.

Summary:

We developed this product which carries new functions, CD( includes MP3CD playback), MagicGate Memory Stick (recording & playback & updating) and HDD (recording & playback), for the first time as a car audio product. This product for the worldwide market is packed into 1DIN size, with standard features (AM/FM Tuner, MOS-FET50Wx4ch amplifier, OrganicEL display, and sound field control DSP) and the new functions. We considered the operation carefully to handle many music files in the HDD easily. We concentrated on making a new field of audio entertainment, and we were the first to introduce this system on the car audio market. - ^ "V850ES/SA2, V850ES/SA3". Renesas Electronics.

- ^ Kochkov, A. (October 2014). "Reversing firmware using radare2 [H2HC]" (PDF).

- ^ V850 Series Development Environment Pamphlet (PDF) (5.00 ed.). Renesas. 2006-02-01.

- ^ "V850E2/Px4". Renesas Electronics.

- ^ Matsuyama, Hideki (April 18, 2003). "V850E2: The High Performance CPU Platform which realize Various Application Systems with Flexible Memory Configurations". www.coolchips.org. COOL Chips VI.

- ^ a b "V850 Family". Renesas Electronics.

- ^ "RH850 Family (Automotive only)". Renesas Electronics.

- ^ a b "Trademark Notice". www.renesas.com. Renesas.

- ^

"Trademark application T2001-067573". 2001-07-25.

Result: application refused

- ^

"V850 Embedded Microcontroller". www.tmdn.org. 2004-12-18.

Result: application refused

- ^ Schmerling, Holger (2006). "AUTOSAR FlexRay driver now available for microcontrollers" (PDF). System@IC News. 2006 (4). NEC Electronics: 3. S2CID 15509410. Archived from the original (PDF) on 2018-03-02.

- ^ V850E/PH2: Hardware (PDF) (1.00 ed.). NEC Electronics. January 2007. p. 33.

- ^ Quick time-to-market with Renesas Synergy Platform and Cool Phoenix 3 (PDF) (1.00 ed.). Renesas. October 2016.

- ^ "TMVIEW: PHOENIX 3". www.tmdn.org.

- ^ a b c d e f V850 FAMILY 32-bit Single-Chip Microcontroller Architecture (PDF) (7th ed.). Renesas Electronics. March 2001.

- ^ "RH何某というのはSHのコアなのですか?" [Does RH-something employ SH core?]. Renesas Rulz - Japan. Renesas Electronics. 2017-03-29.

- ^ "Could anyone please tells me the major differences between the RH850 and V850 families ? | GNU Tools". gcc-renesas.com.

- ^ "PC-FXGA – WIP". Super CD·Rom2 à GoGo. 2015-12-13.

- ^ V810 FAMILY 32-bit Microprocessor Architecture (PDF) (1st ed.). NEC Corporation. October 1995. Archived from the original (PDF) on 2016-12-23. Retrieved 2018-02-02.

- ^ a b c "A newer GCC compiler. « Virtual Boy Development Board « Forum « Planet Virtual Boy". www.planetvb.com.

- ^ a b Pioneer (2007-02-01). Pioneer Car Stereo System AVIC-D3 Service Manual. p. 262.

- ^ Renesas (1999-04-01). V832 32-bit Microprocessor Hardware uPD705102 Preliminary User's Manual. p. 27.

- ^

Suzuki, Hiroaki; Suzuki, Chika; Kimura, Akiko; Sato, Syoichiro; Ide, Syuichi; Sakanaka, Yasuhide (1993-01-22). "A 32 - Bit RISC Microprocessor V810 and its design techniques" (PDF). SIG SLDM Technical Reports. 1992-SLDM-065 (in Japanese). 1993 (6). Information Processing Society of Japan: 155–162. AA11451459.

Abstract:

An advanced 32-bit RISC microprocessor for embedded controls; V810 and its design technique are described in this paper. The V810 is fabricated by using 0.8μm CMOS double metal layer process technology to integrate 240,000 transistors on a 7.7×7.7mm2 die. In design of the V810, we used design automation techniques. The V810 was analyzed for logical correctness and timing constraint before fabrication. Finally, V810 executed realtime-OS and SPEC benchmarks correctly at first silicons. - ^

Akaboshi, Hiroki; Yasuura, Hiroto (8 March 1995). "Design Comparison of Hardware Description Languages in RT Level" (PDF). IPSJ SIG Notes (in Japanese). 1995 (24 (1994-SLDM-074)). Information Processing Society of Japan: 57–64. Retrieved 23 September 2022.

Abstract:

Progress of logic/layout synthesis makes it possible to design circuits by Hardware Description Languages (HDLs). When a designed circuit is small, it is synthesized automatically from HDL description. In this paper, to make it clear what kinds of problems are there in designing a large circuit looks like a processor, we design a processor and some components of it by HDLs in RT level and evaluate circuits synthesized by a logic/layout synthesis tool. - ^ Tamura, K. A. (1989). "Locating functional errors in logic circuits" (PDF). Proceedings of the 1989 26th ACM/IEEE conference on Design automation conference - DAC '89. pp. 185–191. doi:10.1145/74382.74414. ISBN 0897913108. S2CID 2364060.

- ^

Kato, S.; Sasaki, T. (September 1983). FDL: A Structural Behavior Description Language. Elsevier Science Ltd. pp. 137–152. ISBN 978-0444866332.

{{cite book}}:|journal=ignored (help) - ^ Yano, Yoichi (April 2012). "32ビット・マイコン「V60」開発物語" [Development story of the V60; a 32-bit microprocessor] (PDF). Encor (in Japanese) (75). Society of Semiconductor Industry Specialists: 17–20.

- ^ Sutherland, Stuart (2013). The Verilog PLI Handbook: A User's Guide and Comprehensive Reference on the Verilog Programming Language Interface. Springer Science & Business Media. p. 3. ISBN 9781461550174.

- ^ Inasaka, Jun; Ikeda, Rikikazu; Umezawa, Kazuhiko; Yoshikawa, Ko; Yamada, Shitaka; Kitawaki, Shigemune (January 2003). "Hardware Technology of the Earth Simulator" (PDF). NEC Research and Development. Architecture and Hardware for HPC. 44 (1): 27–36.

- ^ "Trademarks". www.mentor.com. Mentor Graphics.

- ^ "Mentor Graphics and Pyxis Technology". www.mentor.com. Mentor Graphics.

- ^ "IC Nanometer Design Tutorials – Santa Clara University". www.mentor.com. Santa Clara University.

- ^

Jansen, Dirk (2010-02-23). The Electronic Design Automation Handbook. Springer Science & Business Media. p. 54. ISBN 9780387735436.

Design Architect by Mentor Graphics Corporation with programs NETED and SYMED. This system is the most universal one of the three [3.3].

Version C1 on HP Unix V10.20 is used (short form MENTOR) - ^ CB-C8 3-VOLT, 0.5-MICRON CELL-BASED CMOS ASIC (PDF) (Report). NEC. July 1994. p. 7. Retrieved 23 September 2022.

- ^ Harlow III, Justin E. (1986). What Every Engineer Should Know about Engineering Workstations. CRC Press. p. 47. ISBN 9780824775094.

- ^ Kang, Sungho. "Verification I" (PDF). A Course Material of Yonsei University.

- ^ Takasaki, S.; Sasaki, T.; Nomizu, N.; Ishikura, H.; Koike, N. (1986). "HAL II: A Mixed Level Hardware Logic Simulation System" (PDF). 23rd ACM/IEEE Design Automation Conference. pp. 581–587. doi:10.1109/DAC.1986.1586146. ISBN 0-8186-0702-5.

- ^ a b c d e f g h i "V810 Seminar" (PDF). NEC Corporation. 1995-02-21.

- ^ a b c d V810 FAMILYTM 32-BIT MICROPROCESSOR ARCHITECTURE (PDF) (1st ed.). NEC Corporation. October 1995. Archived from the original (PDF) on 2016-12-23. Retrieved 2018-02-02.

- ^

Engblom, Jakob (2003). "Embedded Systems Computer Architecture" (PDF). Extended Abstract from ESSES 2003. S2CID 15760973. Archived from the original (PDF) on 2018-02-25.

Code size is an important factor in most embedded designs, and instruction sets are designed and extended with code size in mind. Fairly typically, the NEC V850 architecture uses 16-, 32-, 48-bit, and 64-bit instructions to encode a RISC-style instruction set. The 32-bit ARM and MIPS architecture have been extended with reduced 16-bit instruction sets in order to reduce the code size. Instructions that perform a lot of work, like loading multiple values from the stack, are popular to reduce code size. - ^ "GCC: V850 Options". gcc.gnu.org. Free Software Foundation, Inc.

- ^ Kaneko, Hiroaki; Sakurai, Yoshikazu; Nasu, Masaki; Katsuta, Hiroshi; Nagasaki, Kazunori; Hiiragizawa, Yasunori; Sonobe, Satoru; Onishi, Tatsuro; Tokunaga, Kei (March 1995). "高性能・低消費電力動作の32ビットRISCシングルチップマイクロコンピュータV851" [High Performance and Low-Power-Consumption 32-bit RISC Single Chip Microcomputer V851.]. NEC Technical Journal. Special Issue on Semiconductor Devices. (in Japanese). 48 (3). NEC Corporation: 42–48. ISSN 0285-4139.

- ^ Yamagata, Yasushi; Ishibashi, Takashi; Sano, Yuichi; Koga, Yoshikazu; Yoshida, Miho; Sugo, Akihisa (April 1996). "32ビットRISCマイクロコントローラV853" [32-bit RISC Microcontroller V853.]. NEC Technical Journal. Special Issue: Semiconductor Devices. (in Japanese). 49 (3). NEC Corporation: 55–60. ISSN 0285-4139.

- ^ a b

Krämer, Michael (2011-01-21). "Latest 32-bit RISC architecture for automotive expands functionality". EE Times.

All V850 products are upwards compatible. As a result, today's sophisticated components can still execute the same instructions as their forebears. The architecture has undergone continual improvements with extensions to the instruction set, and today it offers computing power of up to 2.6 Dhrystone MIPS/MHz. Further performance increases can be achieved by integrating several of these processor cores on a single chip, delivering twice or even four times more computing power. - ^ V850E1 for Architecture (PDF) (3.01 ed.). Renesas. 2004-02-01.

- ^ a b "First 32-bit RISC Microcontroller with Integrated Flash Memory Offered by NEC Electronics Newest Product in Company's V800 Series Operates at 33 MHz. - Free Online Library". www.thefreelibrary.com. BUSINESS WIRE. 1996-03-04.

- ^ UPD70F3003A,70F3025A,70F3003A(A) Data Sheet (PDF) (5.01 ed.). Renesas. 2005-08-01. p. 37.

- ^ Matsumoto, Yoichi (1999). "NEXT STEP: NEC'S STRATEGY FOR RISC MICROCOMPUTERS" (PDF). NEC Device Technology International. 1999 (5). NEC.

- ^ a b "NEC Launches 32-Bit RISC Single-chip Microcontroller for Ultra-low-power Mobile Applications". www.nec.co.jp. NEC: Press Release. 2001-08-23.

- ^ "NEC Releases Java Accelerator for 32-Bit RISC V850 Microcontrollers". www.nec.co.jp. NEC. 2001-11-15.

- ^

Aoki, Yayoi (2001-11-30). "US 6,948,034 B2; Method for use of stack" (PDF). pdfpiw.uspto.gov.

The present invention relates to a method for use of a stack in a Java accelerator device.

- ^

Mine, Kazumasa (2000-11-21). "US 7,200,741 B1: Microprocessor having main processor and co-processor" (PDF). pdfpiw.uspto.gov. United States Patent and Trademark Office.

With such arrangement, the microprocessor can flexibly deal with various kinds of instruction sets with different architectures such as an instruction set for an interpreter language for realizing a virtual machine for Java and an instruction set for emulating another microprocessor.

- ^ "NEC Electronics Introduces 32-Bit V850E2/ME3 Microcontroller for High-Performance, Real-Time Processing; Most Advanced V850 Microcontroller Enables Performance of 400MIPS at 200MHz. - Free Online Library". www.thefreelibrary.com. 2005.

- ^ a b "NEC Electronics Introduces Next-Generation V850E2M Dual-Core Architecture For 32-Bit V850 Microcontrollers". www.businesswire.com. Business Wire. 2009-04-20.

- ^ Whytock, Paul (2010-10-14). "Next-Gen 32Bit V850 CPU Core Features SIMD Support". Electronic Design.

- ^ Kumura, Takahiro; Taga, Soichiro; Ishiura, Nagisa; Takeuchi, Yoshinori; Imai, Masaharu (2010-08-16). "Software Development Tool Generation Method Suitable for Instruction Set Extension of Embedded Processors" (PDF). IPSJ Transactions on System LSI Design Methodology. 3. Information Processing Society of Japan: 207–221. doi:10.2197/ipsjtsldm.3.207. ISSN 1882-6687.

- ^ "No matches were found for your search term(s)". Renesas.

- ^

Harigai, Hisao; Kusuda, Masahiro; Kojima, Shingo; Moriyama, Masatoshi; Ienaga, Takashi; Yano, Yoichi (1992-10-22). "A low power consumption and low voltage operation 32-bit RISC Microprocessor" (PDF). SIG ARC Technical Reports (in Japanese). 1992 (82 (1992-ARC-096)). Information Processing Society of Japan: 41–48. AN10096105.

Abstract:

An advanced 32-bit RISC microprocessor for embedded control; V810 is introduced in this paper. The V810 has high performance and application specified functions.

V810 dissipates less power than any other RISC chips. The V810 is the first 32-bit RISC microprocessor that operates at 2.2 V.

The V810 chip is fabricated by using 0.8 μm CMOS double metal layer process technology to integrate 240,000 transistors on a 7.7×7.7 mm2 die. - ^ Kusuda, Masahiro; Hirai, Miho; Suzuki, Hiroaki; Daito, Masayuki; Suzuki, Chika; Kimura, Akiko; Demura, Shigeki; Ishibashi, Takashi; Sato, Syoichiro (September 1992). "低消費電力・低電圧動作のオリジナル32ビットRISCマイクロプロセッサV810" [V810-Low Power Consumption and Low Voltage Operation 32-bit RISC Microprocessor.] (image/jp2). NEC Technical Journal (in Japanese). 45 (8). NEC Corporation: 66–73. ISSN 0285-4139. 000000018731.

- ^ a b c d e Kuwata, Takaaki. "ロジックプロセス シリコンロジックプロセス ロジックプロセスの開発ものがたり" [Development story of silicon logic process] (PDF) (in Japanese). Semiconductor History Museum of Japan. Retrieved 23 September 2022.

- ^ V850/SA1 for Hardware (PDF) (4.01 ed.). Renesas. 2005-08-01.

- ^ OCHI, MASATOSHI; ISHIKAWA, HIROTAKA; TSUJI, NOBUHIRO; TAKEDA, MITSURU; SUTO, SHIN'ICHI; ISHIKAWA, TATSUYA (2001-03-23). "32ビットRISCマイクロコントローラV850/SBXのEMIノイズ低減" [EMI Noise Reduction of 32bit RISC Microcontroller V850/SBX.]. NEC Technical Journal (in Japanese). 54 (3). NEC: 41–44. ISSN 0285-4139.

- ^ V850ES/SA2, V850ES/SA3 32-Bit Single-Chip Microcontrollers Hardware (PDF) (2.01 ed.). Reneas. August 2005.

- ^ a b V850ES/JG3-L User's manual: Hardware (PDF) (9.00 ed.). Renesas. 2014-03-14.

- ^ a b "NEC Announces New Process Technology for World's Most Advanced System LSIs - World's First 0.13-micron Process Technology -". www.nec.co.jp. 1999-10-04.

- ^ "RH850 & RL78 – Next Generation of Automotive Microcontrollers –". slideplayer.com.

- ^ "Using the GNU Compiler Collection (GCC): V850 Options". gcc.gnu.org.

- ^ a b "民生用マルチメディア機器向け32ビットオリジナルRISC型マイクロプロセッサの発売について ~周辺機能を内蔵した32/16ビット・マイクロプロセッサの製品化~". www.nec.co.jp (in Japanese). 1995-03-22. Retrieved 5 February 2018.

- ^ "V810 Architecture Summary" (PDF). www.planetvb.com. Planet Virtual Boy.

From the V810 Seminar.

- ^ a b c

Suzuki, Hiroaki; Sakai, Toshichika; Harigai, Hisao; Yano, Yoichi (1995-04-25). "A 0.9-V, 2.5 MHz CMOS 32-bit Microprocessor". IEICE Transactions on Electronics. E78-C (4): 389–393. ISSN 0916-8516. Retrieved 2018-01-09.

Summary:

A 32-bit RISC microprocessor "V810" that has 5-stage pipeline structure and a 1 Kbyte, direct-mapped instruction cache realizes 2.5 MHz operation at 0.9 V with 2.0 mW power consumption. The supply voltage can be reduced to 0.75 V. To overcome narrow noise margin, all the signals are set to have rail-to-rail swing by pseudo-static circuit technique. The chip is fabricated by a 0.8 μm double metal-layer CMOS process technology to integrate 240,000 transistors on a 7.4 × 7.1 mm die. - ^ a b Turley, Jim (June 2, 1997). "NEC V830 Adds Speed, New Instructions" (PDF). Microprocessor Report. Archived (PDF) from the original on April 24, 2024. Retrieved April 24, 2024.

- ^ a b Nakayama, Naoko; Tsukamoto, Hirokazu. "HIGH-PERFORMANCE 32-BIT RISC MICROPROCESSOR V832" (PDF). NEC Device Technology International. 1998 (51). NEC. Archived from the original (PDF) on February 10, 2018.

- ^ Nadehara, Kouhei; Kuroda, Ichiro; Daito, Masayuki; Nakayama, Takashi (December 1, 1995). "Low-power multimedia RISC". IEEE Micro. 15 (6): 20–29. doi:10.1109/40.476255 – via IEEE Xplore.

- ^ a b "V850 family Product Letter – V851" (PDF). datasheetarchive.com. NEC.

- ^ a b "V850 family Product Letter – V853" (PDF). datasheetarchive.com. NEC.

- ^ a b "世界で初めてフラッシュメモリを内蔵した32ビットRISC型マイクロコントローラの発売について". www.nec.co.jp. 1996-03-12. Retrieved 2018-02-01.

- ^ a b "NEC Releases 32-Bit RISC Single-Chip Microcontrollers Incorporating 3.3-V Flash Memory and Operating at 40 MHz". www.nec.co.jp. 1997-04-08.

- ^ a b "Major Specifications of the V850E CPU Core". www.nec.co.jp. 1997-04-08.

- ^ a b c d e Kimura, Akira (Spring 2000). "CPU CORE FOR SYSTEM LSI V850E/VR4120A" (PDF). NEC Device Technology International. 2000 (57). Archived from the original (PDF) on 2018-02-07.

- ^ a b "KIT-NB85E-TP (-H) SPECIFICATION". Midas lab inc.

- ^ a b c d "KIT-NA85E2-TP (-H) SPECIFICATION". www.midas.co.jp. Midas lab inc.

- ^ a b c d e f SAKURAI, Yoshikazu; SUZUK, Hiroaki; MAEMURA, Kouji; TAKAKURA, Satoshi (December 2006). "Present Status of the Embedded CPU in SoC Design" (PDF). NEC Technical. 1 (5): 38–41.

- ^ a b "Renesas Electronics Announces Development of Next-Generation 32-Bit V850 CPU core with SIMD Support that Provides Enhanced Signal Processing". Renesas Electronics. 2010-10-01.

- ^ a b c d e Design Manual: CB-9 Family VX/VM Type Core Library (PDF) (5th ed.). NEC.

- ^ a b Sugimoto, Hideki; Sakairi, Tetsuya; Matoba, Shoichiro; Akaike, Yukihiki; Matsuyama, Hideki (March 1998). "32ビットRISC CPU V850E搭載コア「NA85E」" [32bit RISC CPU Core "NA85E".]. NEC Technical Journal. Special Issue: Semiconductor Devices. Semiconductor Devices for Computers Systems. Microcomputers. (in Japanese). 51 (3): 36–39. ISSN 0285-4139.

- ^ a b Sugimoto, Hideki; Ikeuchi, Tooru (2000-03-30). "32ビツトRISC CPU V850E搭載コア「NB85E」 32bit RISC CPU Core "NB85E"" [32bit RISC CPU Core "NB85E".]. NEC Technical Journal. Special Issue: Semiconductor Devices; Basic Technology (in Japanese). 53 (4). NEC: 159–162. ISSN 0285-4139. 200902106221942927.

- ^ Sugimoto, Hideki (2001-03-23). "RISCプロセッサNx85E2 CPU" [RISC Processor Nx85E2 CPU.]. NEC Technical Journal (in Japanese). 54 (3). NEC: 30–33. ISSN 0285-4139.

- ^ "dNTSC". The Free Dictionary.

- ^ Simovich, Slobodan; Radivojevic, Ivan P.; Endres, T. J.; Bentson, Tom; Bingham, Ray; Blair, Tony; Cowling, Tom; Eylander, Mark; Fagan, Rory; Long, Chris; Longino, Jim; Olson, Dan; Subia, Rollen; Whitcomb, Doug (2003). "ReX: A dNTSC Receiver System-on-Chip" (PDF). HotChips15 Presentation. 15th. HotChips: 9–10.

- ^ NEC Electronics (July 2004). V850E2 32-bit Microprocessor Core Architecture (PDF) (Preliminary ed.). pp. 230–233.

- ^ "32-Bit Microcontrollers V850/ME3 Usage Restrictions" (PDF). 2006-11-02.

- ^ a b "NEC Breaks the 0.10-micron Barrier with CB-130 Cell-Based IC Family and UX5 Process Technology". www.nec.co.jp. 2000-10-30.

- ^ a b "Core Lineup and List of Specifications for CB-130". www.nec.co.jp. 2000-10-30.

- ^ a b "NEC Licenses V850E Microprocessor Core to Synopsys – Agreement Provides 25,000 Synopsys-Registered Designers Access to CPU Core for SoC Development –". nec.co.jp. NEC Corporation. 2010-10-01.

- ^ a b "Synopsys DesignWare IP Enables Full-Service SoC Design Foundry for Global UniChip". Synopsys.

- ^ "V851 32-BIT RISC MICROCONTROLLER CORE" (PDF). 4donline.ihs.com. NEC. 1998.

- ^ "V853 32-BIT MICROCONTROLLER CORE" (PDF). 4donline.ihs.com. NEC. 1997.

- ^ a b c d e f g h i PARTNER Users Manual V800 Series "NB85E-TP Part Edition" (PDF) (2.13 ed.). Midas Lab. Inc. 2003-12-10.

- ^ a b c d e f g h KIT-NB85E-TP User's Manual (PDF) (3.14 ed.). Midas Lab. Co., Ltd. 2003-05-12.

- ^ a b c d e f g h i j Kimura, Akira (2000). "CPU CORE FOR SYSTEM LSI V850E/VR4120A" (PDF). NEC Device Technology International. 2000 (57). NEC.

- ^ a b c d NU85E 32-Bit Microprocessor Core Hardware: NU85E, NU85EA (PDF) (3rd ed.). NEC. March 2002.

- ^ a b c Memory Controller NT85E500, NDT85E500V10, NT85E502 (PDF) (3rd ed.). NEC. September 2002.

- ^ a b c d e Memory Controller NA85E535, NBA85E535Vxx (PDF) (2nd ed.). NEC. October 2002.

- ^ a b KIT-NA85E2-TP(-H) ユーザーズ・マニュアル (PDF) (in Japanese). Midas Lab. Co., Ltd. 2006-01-05. p. 1.00.

- ^

"NEC narrows gate length below 0.10 micron | EE Times". EETimes. 2000-10-31.

NEC also will provide internally-developed V850E and VRx CPUs, though Mabuchi said he believes NEC will need to license the ARM9 core to address the market for mobile terminals. - ^ Matsui, Kenji. "RISC MICROCOMPUTER REFERENCE PLATFORM" (PDF). NEC Device Technology International. 2000 (58). NEC.

- ^

"NEC Electronics Achieves Key Milestone in ACE-2 Initiative;Reduces System-Level Turnaround Time by More Than 30 Percent

Company Also Unveils Second Phase of Its Open System Design Methodology". www.nec.co.jp. NEC: Press Release. 2000-05-15. - ^ Nishiguchi, Nobuyuki (2001-02-02). "システムLSIの未来は、NECが拓く –設計環境の現状と今後–" [System LSI Design Envilonments, Today and the Future] (PDF) (in Japanese). NEC Corporation.

- ^ YAMADA, Kazuo; NISHIMOTO, Hiroaki; DAITO, Masayuki; ONO, Hirohiko (December 2007). "Processor Design Verification Using the Hybrid Emulator" (PDF). NEC Technical Journal. 2 (4): 51–55.

- ^ "PFESiP EP-1 Evaluation Board". datasheetarchive.com (in Japanese). Renesas. August 2008.

- ^

PFESiP EP-1 Evaluation Board Lite 技術情報編 (PDF) (in Japanese) (1st ed.). Renesas Electronics. September 2008.

A19354JJ1V1UM00

- ^

"PFESiP(Platform for Embedded System in a Package)EP Series EP-3" (PDF) (in Japanese). Renesas. May 2010.

V850E2M CPU core,max. 266 MHz operation

- ^ "Companion Chip Reference FPGA Designs". www.logicbricks.com.

- ^ "Xylon logiCRAFT-CC Development Kits Accelerate Development of FPGA Companion Chips for Popular Embedded Processors". www.chipestimate.com.

- ^ "Renesas Electronics Introduces 4th-Generation V850 Microcontrollers Series with 74 Individual Devices for Automotive Body, Dashboard, Chassis and Safety Applications" (Press release). Renesas. 2010-11-04.

- ^ "Renesas - New MCUs for automotive body, dashboard, chassis and safety applications". www.electropages.com.

- ^ "V850ES/Fx3". Renesas Electronics. Retrieved 2018-01-28.

- ^ "V850E2/Jx4 Series Ultra Low Power 32 bit MCUs – Migration from V850ES/Jx3 MCUs –" (PDF). Renesas.

- ^ "V850/Jx4 Series Ultra Low Power 32 bit MCUs" (PDF). Renesas. March 2012.

- ^ Yano, Y.; Koumoto, Y.; Sato, Y. (1988). "V60/V70 microprocessor and its systems support functions". Digest of Papers. COMPCON Spring 88 Thirty-Third IEEE Computer Society International Conference. pp. 36–42. doi:10.1109/CMPCON.1988.4824. ISBN 0-8186-0828-5. S2CID 9186701.

- ^

Mizuhashi, Yukiko; Teramoto, Msanoro (August 1989). "Real-time UNIX operating system: RX-UX 832". Microprocessing and Microprogramming. 27 (1–5): 533–538. doi:10.1016/0165-6074(89)90105-1.

Abstract: