Intel 5 Series

Intel 5 Series is a computing architecture introduced in 2008 that improves the efficiency and balances the use of communication channels in the motherboard. The architecture consists primarily of a central processing unit (CPU) (connected to the graphics card and memory) and a single chipset (connected to motherboard components). All motherboard communications and activities circle around these two devices.

The architecture is a product of adjustments made to the Intel 4 Series to deliver higher performance motherboards while maintaining efficiency and low power. The changes revolve around chipset and processor design, in conjunction with a rearrangement of functions and controllers. The result is the first major change in many years of computing.

Design concept

[edit]

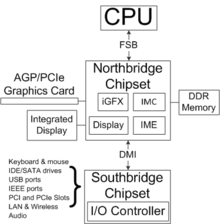

The concept of the architecture was to improve motherboard mechanics to keep pace with the CPU as it gained more speed and multiplied in number of cores. In the previous architecture, the CPU was communicating heavily with the motherboard's central component, the Northbridge chipset, as it was the intermediary between the CPU, memory, and, in most cases, graphics card. The CPU would communicate with the Northbridge chipset when it needed data from the memory or when it needed to output graphics to the display. This arrangement caused the communication channel known as the front-side bus (FSB) to be heavily used. It was not long till either the FSB would reach full capacity or operate inefficiently with more cores. With the memory controller and/or graphics core moved into the processor, the reliance of separate motherboard chipsets for these functions are reduced.

Ibex Peak

[edit]

The Ibex Peak chipset includes only Platform Controller Hub (PCH) per model, which provides peripheral connections, and display controllers for CPU with integrated graphics via Flexible Display Interface (excluding P-models). Additionally, the PCH is connected to the CPU via Direct Media Interface (DMI).

Taking advantage of Nehalem CPUs with integrated graphics and PCI Express ports, the Intel Management Engine (ME) and a display controller for integrated graphics, once housed in north bridge, are moved into the Platform Controller Hub (PCH). The I/O Controller Hub (ICH) function is integrated into the PCH, removing the need for separate north bridge and south bridge.

| Chipset | Code Name | sSpec Number | Part numbers | Release Date | Bus Interface | Link Speed[a] | PCI Express lanes | PCI | SATA | USB | FDI support | TDP |

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 3 Gbit/s | v2.0 | |||||||||||

| H55 | Ibex Peak[1][2] | SLGZX(B3) | BD82H55 (PCH) | Jan 2010 | DMI | 2 GB/s | 6 PCIe 2.0 at 2.5 GT/s | Yes | 6 ports | 12 ports | Yes | 5.2 W |

| P55 | SLH24 (B3), SLGWV (B2) |

BD82P55 (PCH) | Sep 2009 | 8 PCIe 2.0 at 2.5 GT/s | 14 ports | No | 4.7 W | |||||

| H57 | SLGZL(B3) | BD82H57 (PCH) | Jan 2010 | Yes | 5.2 W | |||||||

| Q57 | SLGZW(B3) | BD82Q57 (PCH) | 5.1 W |

| Model | Top marking |

|---|---|

| PM55 Express | BD82PM55 |

| QM57 Express | BD82QM57 |

| HM55 Express | BD82HM55 |

| HM57 Express | BD82HM57 |

| QS57 Express | BD82QS57 |

| Model | Top marking | Fab | ME Firmware Version | PCIe |

|---|---|---|---|---|

| 3400 | BD3400 | 65 nm | 6.0 | 2.0 |

| 3420 | BD3420 | |||

| 3450 | BD3450 |

Tylersburg

[edit]The Tylersburg family of chipsets is for Socket LGA 1366 supporting CPUs with triple channel memory controllers. Unlike the Ibex Peak chipsets, The Tylersburg family of chipsets do not include the PCH, and the I/O Hub mainly provides extra PCI Express 2.0 ports. Peripheral connections are provided by I/O Controller Hub (ICH) connected to the DMI interface. Intel 5 series IOH support ICH10, while Intel 5500 Series IOH support ICH9 or ICH10.

Single socket Nehalem-based chipset

[edit]| Chipset | Code Name | sSpec Number | Part numbers | Release Date | Socket | Bus Interface | PCI Express lanes | PCI | Intel VT-d support | SATA | USB | FDI support | TDP | ||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 6 Gbit/s | 3 Gbit/s | v3.0 | v2.0 | ||||||||||||

| X581 | Tylersburg | SLGBT (B2), SLGMX (B3), SLH3M (C2) |

AC82X58 (IOH) | November 2008 | LGA 1366 | QPI | 36× PCIe 2.0 (IOH); 6× PCIe 1.1 (ICH) |

Yes | Yes | None | 6 ports | None | 12 ports | No | 28.6 W2 |

- 1 Nehalem moves the memory controller into the processor, thereby obsoleting the north bridge. Despite that, LGA 1366 still features a north and a south bridge. The X58 IOH acts as a bridge from the QPI to PCI Express peripherals and DMI to the ICH10/ICH10R southbridge.

- 2 X58 TDP includes the X58 IOH TDP in addition to the ICH10/ICH10R TDP.

Dual socket Nehalem-based Xeon chipsets

[edit]The Nehalem-based Xeons for dual-socket systems, initially launched as the Xeon 55xx series, feature a very different system structure: the memory controllers are on the CPU, and the CPUs can communicate with one another as peers without going via the chipset. This means that the 5500 and 5520 (initial codename Tylersburg-EP) chipsets are essentially QPI to PCI Express interfaces; the 5520 is more intended for graphical workstations and the 5500 for servers that do not need vast amounts of PCI Express connectivity

| Launch name | Codename | QPI ports | QPI speed | Fast I/O | IOCH | Other features | Top marking |

|---|---|---|---|---|---|---|---|

| 5500 | Tylersburg-24S, Tylersburg-24D[3] |

1, 2 |

4.8, 5.86 or 6.4 GT/s | 1 ×16 PCIe Gen 2, 2 ×4 PCIe Gen 1 to talk to southbridge | ICH10 (ICH9 also possible) | Integrated Management Engine with its own 100 Mbit Ethernet[4] | AC5500 SLGMT 901036 (B-3), AC5500 SLH3N 904728 (C-2) |

| 5520 | Tylersburg-36S, Tylersburg-36D |

1, 2 |

4.8, 5.86 or 6.4 GT/s | 2 ×16 PCIe Gen 2, 1 ×4 PCIe Gen 1 to talk to southbridge | ICH10 (ICH9 also possible) | Integrated Management Engine with its own 100 Mbit Ethernet[4] | AC5520 SLGMU 901037 (B-3), AC5520 SLH3P 904729 (C-2) |

See also

[edit]Notes

[edit]- ^ Aggregated speed for both directions

References

[edit]- ^ Intel 5 Series Chipset

- ^ Mobile Intel 5 Series Chipset

- ^ "Intel X58 Extreme DX58SO motherboard review". Guru3D.com. Retrieved 30 April 2023.

- ^ a b "Intel® 5520 Chipset and Intel® 5500 Chipset" (PDF). intel.com. March 2009. Retrieved 30 April 2023.

External links

[edit]Ibex Peak

[edit]- Intel 5 series: H55, H57, P55, Q57

- Mobile Intel 5 series: HM55, HM57, PM55, QM57, QS57

- Intel 3400 and 3420 Chipsets Overview

- Intel 5 Series Chipset and Intel 3400 Series Chipset

- Support for the Intel 5 Series Chipset

- Intel's "Ibex Peak"

Tylersburg

[edit]- Intel X58 Express Chipset

- Intel 5500 series: 5500, 5520

- Intel 5500 and 5520 Chipset