Epyc

| |

| General information | |

|---|---|

| Launched | June 20, 2017 |

| Marketed by | AMD |

| Designed by | AMD |

| Common manufacturers |

|

| Performance | |

| Max. CPU clock rate | 2.7 GHz to 5.0 GHz |

| Architecture and classification | |

| Technology node | 14 nm to 3 nm |

| Microarchitecture | |

| Instruction set | AMD64 (x86-64) |

| Extensions | |

| Physical specifications | |

| Cores |

|

| Memory (RAM) |

|

| Socket | |

| Products, models, variants | |

| Core names |

|

| History | |

| Predecessor | Opteron |

Epyc (stylized as EPYC) is a brand of multi-core x86-64 microprocessors designed and sold by AMD, based on the company's Zen microarchitecture. Introduced in June 2017, they are specifically targeted for the server and embedded system markets.[1]

Epyc processors share the same microarchitecture as their regular desktop-grade counterparts, but have enterprise-grade features such as higher core counts, more PCI Express lanes, support for larger amounts of RAM, and larger cache memory. They also support multi-chip and dual-socket system configurations by using the Infinity Fabric interconnect.

History

[edit]In March 2017, AMD announced plans to re-enter the server market with a platform based on the Zen microarchitecture, codenamed Naples, and officially revealed it under the brand name Epyc in May.[2] That June AMD officially launched Epyc 7001 series processors, offering up to 32 cores per socket, and enabling performance that allowed Epyc to be competitive with the competing Intel Xeon Scalable product line.[3] In August 2019, the Epyc 7002 "Rome" series processors, based on the Zen 2 microarchitecture, launched, doubling the core count per socket to 64, and increasing per-core performance dramatically over the last generation architecture.

In March 2021, AMD launched the Epyc 7003 "Milan" series, based on the Zen 3 microarchitecture.[4] Epyc Milan brought the same 64 cores as Epyc Rome, but with much higher per-core performance, with the Epyc 7763 beating the Epyc 7702 by up to 22 percent despite having the same number of cores and threads.[5] A refresh of the Epyc 7003 "Milan" series with 3D V-Cache, named Milan-X, launched on March 21, 2022, using the same cores as Milan, but with an additional 512 MB of cache stacked onto the compute dies, bringing the total amount of cache per CPU to 768 MB.[6]

In September 2021, Oak Ridge National Laboratory partnered with AMD and HPE Cray to build Frontier, a supercomputer with 9,472 Epyc 7453 CPUs and 37,888 Instinct MI250X GPUs, becoming operational by May 2022. As of November 2023, it is the most powerful supercomputer in the world according to the TOP500, with a peak performance of over 1.6 exaFLOPS.

In November 2021, AMD detailed the upcoming generations of Epyc, and unveiled the new LGA-6096 SP5 socket that would support the new generations of Epyc chips. Codenamed Genoa, these CPUs are based on the Zen 4 microarchitecture and built on TSMC's N5 node, supporting up to 96 cores and 192 threads per socket, alongside 12 channels of DDR5[7] and 128 PCIe 5.0 lanes. Genoa also became the first x86 server CPU to support Compute Express Link 1.1,[8] or CXL, allowing for further expansion of memory and other devices with a high bandwidth interface built on PCIe 5.0. AMD also shared information regarding the sister chip of Genoa, codenamed Bergamo. Bergamo is based on a modified version of Zen 4 named Zen 4c, designed to allow for much higher core counts and efficiency at the cost of lower single-core performance, targeting cloud providers and workloads, compared to traditional high performance computing workloads.[9] It is compatible with Socket SP5, and supports up to 128 cores and 256 threads per socket.[10]

In November 2022, AMD launched their 4th generation Epyc "Genoa" series of CPUs. Some tech reviewers and customers had already received hardware for testing and benchmarking, and third party benchmarks of Genoa parts were immediately available. The flagship part, the 96 core Epyc 9654, set records for multi-core performance, and showed up to 4× performance compared to Intel's flagship part, the Xeon Platinum 8380. High memory bandwidth and extensive PCIe connectivity removed many bottlenecks, allowing all 96 cores to be utilized in workloads where previous generation Milan chips would have been I/O-bound.

In June 2023, AMD began shipping the 3D V-Cache enabled Genoa-X lineup, a variant of Genoa that uses the same 3D die stacking technology as Milan-X to enable up to 1152 MB of L3 cache, a 50% increase over Milan-X, which had a maximum of 768 MB of L3 cache.[11] On the same day, AMD also announced the release of their cloud optimized Zen 4c SKUs, codenamed Bergamo, offering up to 128 cores per socket, utilizing a modified version of the Zen 4 core that was optimized for power efficiency and to reduce die space. Zen 4c cores do not have any instructions removed compared to standard Zen 4 cores; instead, the amount of L3 cache per CCX is reduced from 32 MB to 16 MB, and the frequency of the cores is reduced.[12] Bergamo is socket compatible with Genoa, using the same SP5 socket and supporting the same CXL, PCIe, and DDR5 capacity as Genoa.[13]

In September 2023, AMD launched their low power and embedded 8004 series of CPUs, codenamed Siena. Siena utilizes a new socket, called SP6, which has a smaller footprint and pin count than the SP5 socket of its contemporary Genoa processors. Siena utilizes the same Zen 4c core architecture as Bergamo cloud native processors, allowing up to 64 cores per processor, and the same 6 nm I/O die as Bergamo and Genoa, although certain features have been cut down, such as reducing the memory support from 12 channels of DDR5 to only 6, and removing dual socket support.[14]

In May 2024, AMD launched the new 4004 series of CPUs, codenamed Raphael. Sharing the same AM5 socket as desktop Ryzen CPUs. In contrast to desktop parts ECC memories are supported. AM5 motherboard manufacturers do not support the 4004 so available options are very limited to devices which are not suitable for desktop use.

In October 10th, 2024, AMD launched the new 9005 series of CPUs, codenamed Turin. Sharing the same SP5 socket as Genoa and Bergamo, Turin came with numerous platform advancements, including the support for up to 6400 MT/s DDR5 memory.[15] Turin also increased the core count and frequency offerings, with Turin offering 128 Zen 5 cores per socket, and Turin Dense offering 192 Zen 5c cores per socket. And with the highest frequency SKU (The EPYC 9575F) having a operating frequency of up to 5 GHz.[16]

AMD Epyc CPU codenames follow the naming scheme of Italian cities, including Milan, Rome, Naples, Genoa, Bergamo, Siena, Turin and Venice.

| Gen | Year | Codename | Product line | Cores | Socket | Memory |

|---|---|---|---|---|---|---|

| Server | ||||||

| 1st | 2017 | Naples | 7001 series | 32 × Zen | SP3 (LGA) | DDR4 |

| 2nd | 2019 | Rome | 7002 series | 64 × Zen 2 | ||

| 3rd | 2021 | Milan | 7003 series | 64 × Zen 3 | ||

| 2022 | Milan-X | |||||

| 4th | Genoa | 9004 series | 96 × Zen 4 | SP5 (LGA) | DDR5 | |

| 2023 | Genoa-X | |||||

| Bergamo | 128 × Zen 4c | |||||

| Siena | 8004 series | 64 × Zen 4c | SP6 (LGA) | |||

| 2024 | Raphael | 4004 series | 16 × Zen 4 | AM5 (LGA) | ||

| 5th | 2024 | Turin | 9005 series | 128 × Zen 5 | SP5 (LGA) | |

| Turin Dense | 192 × Zen 5c | |||||

| 6th | TBA | Venice | TBA | TBA | SP7 (LGA) | TBA |

| Embedded | ||||||

| 1st | 2018 | Snowy Owl | Embedded 3001 series | 16 × Zen | SP4 (BGA) | DDR4 |

| 2nd | 2019 | Naples | Embedded 7001 series | 32 × Zen | SP3 (BGA) | |

| 3rd | 2021 | Rome | Embedded 7002 series | 64 × Zen 2 | ||

| 4th | 2023 | Genoa | Embedded 9004 series | 96 × Zen 4 | SP5 (BGA) | DDR5 |

Design

[edit]

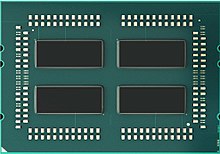

Epyc CPUs use a multi-chip module design to enable higher yields for a CPU than traditional monolithic dies. First generation Epyc CPUs are composed of four 14 nm compute dies, each with up to 8 cores.[22][23] Cores are symmetrically disabled on dies to create lower binned products with fewer cores but the same I/O and memory footprint. Second and Third gen Epyc CPUs are composed of eight compute dies built on a 7 nm process node, and a large input/output (I/O) die built on a 14 nm process node.[24] Third gen Milan-X CPUs use advanced through-silicon-vias to stack an additional die on top of each of the 8 compute dies, adding 64 MB of L3 cache per die.[25]

Epyc CPUs supports both single socket and dual socket operation. In a dual socket configuration, 64 PCIe lanes from each CPU are allocated to AMD's proprietary Infinity Fabric interconnect to allow for full bandwidth between both CPUs.[26] Thus, a dual socket configuration has the same number of usable PCIe lanes as a single socket configuration. First generation Epyc CPUs had 128 PCIe 3.0 lanes, while second and third generation had 128 PCIe 4.0 lanes. All current Epyc CPUs are equipped with up to eight channels of DDR4 at varying speeds, though next gen Genoa CPUs are confirmed by AMD to support up to twelve channels of DDR5.[7][27]

Unlike Opteron, Intel equivalents and AMD's desktop processors (excluding Socket AM1), Epyc processors are chipset-free - also known as system on a chip. That means most features required to make servers fully functional (such as memory, PCI Express, SATA controllers, etc.) are fully integrated into the processor, eliminating the need for a chipset to be placed on the mainboard. Some features may require the use of additional controller chips to utilize.

Reception

[edit]Initial reception to Epyc was generally positive.[27] Epyc was generally found to outperform Intel CPUs in cases where the cores could work independently, such as in high-performance computing and big-data applications. First generation Epyc fell behind in database tasks compared to Intel's Xeon parts due to higher cache latency.[27] In 2021 Meta Platforms selected Epyc chips for its metaverse data centers.[28]

Epyc Genoa was well received, as it offered improved performance and efficiency compared to previous offerings, though received some criticism for not having 2 DIMMs per channel configurations validating, with some reviewers calling it an "incomplete platform".[29]

List of Epyc processors

[edit]Server

[edit]First generation Epyc (Naples)

[edit]The following table lists the devices using the first generation design.

A "P" suffix denotes support for only a single socket configuration. Non-P models use 64 PCIe lanes from each processor for the communication between processors.

EPYC 7001 series

[edit]Common features:

- SP3 socket

- Zen microarchitecture

- GloFo 14 nm process

- MCM with four System-on-a-chip (SOC) dies, two core complexes (CCX) per SOC die[30]

- Eight-channel DDR4-2666 (the 7251 model is limited to DDR4-2400)

- 128 PCIe 3.0 lanes per socket, 64 of which are used for Infinity Fabric in 2P platforms

- 7001P series models are restricted to uniprocessor operation (1P)

| Model[i] | Cores (threads) |

Chiplets | Core config[ii] |

Clock rate | Cache | TDP | Release | Embedded options[iii] | |||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Base (GHz) |

Boost (GHz) | L2 (per core) |

L3 (per CCX) |

Total | Date | Price | |||||||

| All–core | Max | ||||||||||||

| 7251[31][32] | 8 (16) | 4[30] | 8 × 1 | 2.1 | 2.9 | 2.9 | 512 KiB | 4 MiB | 36 MiB | 120 W | Jun 2017[33] | $475 | Yes |

| 7261[31][34] | 2.5 | 8 MiB | 68 MiB | 155/170 W | Jun 2018[35] | $570 | Yes | ||||||

| 7281[31][32] | 16 (32) | 8 × 2 | 2.1 | 2.7 | 2.7 | 4 MiB | 40 MiB | 155/170 W | Jun 2017[33] | $650 | Yes | ||

| 7301[31][32] | 2.2 | 8 MiB | 72 MiB | $800 | Yes | ||||||||

| 7351P[31][32] | 2.4 | 2.9 | 2.9 | $750 | 735P | ||||||||

| 7351[31][32] | $1,100 | Yes | |||||||||||

| 7371[31][36] | 3.1 | 3.6 | 3.8 | 200 W | Nov 2018[37] | $1,550 | Yes | ||||||

| 7401P[31][32] | 24 (48) | 8 × 3 | 2.0 | 2.8 | 3.0 | 8 MiB | 76 MiB | 155/170 W | Jun 2017[33] | $1,075 | 740P | ||

| 7401[31][32] | $1,850 | Yes | |||||||||||

| 7451[31][32] | 2.3 | 2.9 | 3.2 | 180 W | $2,400 | Yes | |||||||

| 7501[31][32] | 32 (64) | 8 × 4 | 2.0 | 2.6 | 3.0 | 8 MiB | 80 MiB | 155/170 W | $3,400 | Yes | |||

| 7551P[31][32] | 2.55 | 180 W | $2,100 | 755P | |||||||||

| 7551[31][32] | $3,400 | Yes | |||||||||||

| 7571[38][39] | 2.2 | 3.0 | 200 W | Nov 2018 | OEM/AWS | -- | |||||||

| 7601[31][32] | 2.7 | 3.2 | 180 W | Jun 2017[33] | $4,200 | Yes | |||||||

- ^ Models with "P" suffixes are uniprocessors, only available as single socket configuration.

- ^ Core Complexes (CCX) × cores per CCX

- ^ Epyc embedded 7001 series models have identical specifications as Epyc 7001 series.

Second generation Epyc (Rome)

[edit]

In November 2018, AMD announced Epyc 2 at their Next Horizon event, the second generation of Epyc processors codenamed "Rome" and based on the Zen 2 microarchitecture.[40] The processors feature up to eight 7 nm-based "chiplet" processors with a 14 nm-based IO chip providing 128 PCIe 4.0 lanes in the center interconnected via Infinity Fabric. The processors support up to 8 channels of DDR4 RAM up to 4 TB, and introduce support for PCIe 4.0. These processors have up to 64 cores with 128 SMT threads per socket.[41] The 7 nm "Rome" is manufactured by TSMC.[24] It was released on August 7, 2019.[42] It has 39.5 billion transistors.[43]

In April 2020, AMD launched three new SKUs using Epyc’s 7nm Rome platform. The three processors introduced were the eight-core Epyc 7F32, the 16-core 7F52 and the 24-core 7F72, featuring base clocks up to 3.7 GHz (up to 3.9 GHz with boost) within a TDP range of 180 to 240 watts. The launch was supported by Dell EMC, Hewlett Packard Enterprise, Lenovo, Supermicro, and Nutanix.[44]

EPYC 7002 series

[edit]Common features:

- SP3 socket

- Zen 2 microarchitecture

- TSMC 7 nm process for the compute dies, GloFo 14 nm process for the I/O die

- MCM with one I/O Die (IOD) and multiple Core Complex Dies (CCD) for compute, two core complexes (CCX) per CCD chiplet

- Eight-channel DDR4-3200

- 128 PCIe 4.0 lanes per socket, 64 of which are used for Infinity Fabric in 2P platforms

| Model | Cores (threads) |

Chiplets | Core config[i] |

Clock rate | Cache | Socket | Scaling | TDP | Release date |

Release price | |||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Base (GHz) |

Boost (GHz) |

L2 (per core) |

L3 (per CCX) |

Total | |||||||||

| 7232P | 8 (16) | 2 + IOD | 4 × 2 | 3.1 | 3.2 | 512 KiB | 8 MiB | 36 MiB | SP3 | 1P | 120 W | Aug 7, 2019 | $450 |

| 7252 | 4 × 2 | 3.1 | 3.2 | 16 MiB | 68 MiB | 2P | $475 | ||||||

| 7262 | 4 + IOD | 8 × 1 | 3.2 | 3.4 | 132 MiB | 155 W | $575 | ||||||

| 7F32 | 8 × 1 | 3.7 | 3.9 | 132 MiB | 180 W | Apr 14, 2020[45] | $2100 | ||||||

| 7272 | 12 (24) | 2 + IOD | 4 × 3 | 2.9 | 3.2 | 16 MiB | 70 MiB |

2P | 120 W | Aug 7, 2019 | $625 | ||

| 7282 | 16 (32) | 2 + IOD | 4 × 4 | 2.8 | 3.2 | 16 MiB | 72 MiB |

$650 | |||||

| 7302P | 4 + IOD | 8 × 2 | 3 | 3.3 | 136 MiB | 1P | 155 W | $825 | |||||

| 7302 | 2P | $978 | |||||||||||

| 7F52 | 8 + IOD | 16 × 1 | 3.5 | 3.9 | 264 MiB | 240 W | Apr 14, 2020[45] | $3100 | |||||

| 7352 | 24 (48) | 4 + IOD | 8 × 3 | 2.3 | 3.2 | 16 MiB | 140 MiB |

2P | 155 W | Aug 7, 2019 | $1350 | ||

| 7402P | 2.8 | 3.35 | 1P | 180 W | $1250 | ||||||||

| 7402 | 2P | $1783 | |||||||||||

| 7F72 | 6 + IOD | 12 × 2 | 3.2 | 3.7 | 204 MiB | 240 W | Apr 14, 2020[45] | $2450 | |||||

| 7452 | 32 (64) | 4 + IOD | 8 × 4 | 2.35 | 3.35 | 16 MiB | 144 MiB |

2P | 155 W | Aug 7, 2019 | $2025 | ||

| 7502P | 2.5 | 3.35 | 1P | 180 W | $2300 | ||||||||

| 7502 | 2P | $2600 | |||||||||||

| 7542 | 2.9 | 3.4 | 225 W | $3400 | |||||||||

| 7532 | 8 + IOD | 16 × 2 | 2.4 | 3.3 | 272 MiB | 200 W | $3350 | ||||||

| 7552 | 48 (96) | 6 + IOD | 12 × 4 | 2.2 | 3.3 | 16 MiB | 216 MiB | 2P | 200 W | $4025 | |||

| 7642 | 8 + IOD | 16 × 3 | 2.3 | 3.3 | 280 MiB | 225 W | $4775 | ||||||

| 7662 | 64 (128) | 8 + IOD | 16 × 4 | 2.0 | 3.3 | 16 MiB | 288 MiB | 2P | 225 W | $6150 | |||

| 7702P | 2 | 3.35 | 1P | 200 W | $4425 | ||||||||

| 7702 | 2P | $6450 | |||||||||||

| 7742 | 2.25 | 3.4 | 225 W | $6950 | |||||||||

| 7H12 | 2.6 | 3.3 | 280 W | Sep 18, 2019 | --- | ||||||||

- ^ Core Complexes (CCX) × cores per CCX

Third generation Epyc (Milan)

[edit]At the HPC-AI Advisory Council in the United Kingdom in October 2019, AMD stated specifications for Milan, Epyc chips based on the Zen 3 microarchitecture.[46] Milan chips will use Socket SP3, with up to 64 cores on package, and support eight-channel DDR4 RAM and 128 PCIe 4.0 lanes.[46] It also announced plans for the subsequent generation of chips, codenamed Genoa, that will be based on the Zen 4 microarchitecture and use Socket SP5.[46]

Milan CPUs were launched by AMD on March 15, 2021.[47]

Milan-X CPUs were launched March 21, 2022.[6] They use 3D V-Cache technology to increase the maximum L3 cache per socket capacity from 256 MB to 768 MB.[48][49][50]

EPYC 7003 series

[edit]Common features:

- SP3 socket

- Zen 3 microarchitecture

- TSMC 7 nm process for the compute and cache dies, GloFo 14 nm process for the I/O die

- MCM with one I/O Die (IOD) and multiple Core Complex Dies (CCD) for compute, one core complex (CCX) per CCD chiplet

- Eight-channel DDR4-3200

- 128 PCIe 4.0 lanes per socket, 64 of which are used for Infinity Fabric in 2P platforms

- 7003X series models include 64 MiB L3 cache dies stacked on top of the compute dies (3D V-Cache)

- 7003P series models are restricted to uniprocessor operation (1P)

| Model | Cores (threads) |

Chiplets | Core config [i] |

Clock rate | Cache | Socket | Scaling | TDP default (range) |

Release price | |||

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Base (GHz) |

Boost (GHz) |

L2 (per core) |

L3 (per CCX) |

Total | ||||||||

| 7203(P) | 8 (16) | 2 + IOD | 2 × 4 | 2.8 | 3.4 | 512 KiB | 32 MiB | 68 MiB | SP3 | 2P (1P) | 120 W (120-150) | $348 ($338) |

| 72F3 | 8 + IOD | 8 × 1 | 3.7 | 4.1 | 260 MiB | 2P | 180 W (165-200) | $2468 | ||||

| 7303(P) | 16 (32) | 2 + IOD | 2 × 8 | 2.4 | 3.4 | 32 MiB | 72 MiB | 2P (1P) | 130 W (120-150) | $604 ($594) | ||

| 7313(P) | 4 + IOD | 4 × 4 | 3.0 | 3.7 | 136 MiB | 2P (1P) | 155 W (155-180) | $1083 ($913) | ||||

| 7343 | 3.2 | 3.9 | 2P | 190 W (165-200) | $1565 | |||||||

| 73F3 | 8 + IOD | 8 × 2 | 3.5 | 4.0 | 264 MiB | 240 W (225-240) | $3521 | |||||

| 7373X | 8* + IOD | 3.05 | 3.8 | 96 MiB | 776 MiB | 240 W (225-280) | $4185 | |||||

| 7413 | 24 (48) | 4 + IOD | 4 × 6 | 2.65 | 3.6 | 32 MiB | 140 MiB | 2P | 180 W (165-200) | $1825 | ||

| 7443(P) | 2.85 | 4.0 | 2P (1P) | 200 W (165-200) | $2010 ($1337) | |||||||

| 74F3 | 8 + IOD | 8 × 3 | 3.2 | 4.0 | 268 MiB | 2P | 240 W (225-240) | $2900 | ||||

| 7473X | 8* + IOD | 2.8 | 3.7 | 96 MiB | 780 MiB | 240 W (225-280) | $3900 | |||||

| 7453 | 28 (56) | 4 + IOD | 4 × 7 | 2.75 | 3.45 | 16 MiB | 78 MiB | 2P | 225 W (225-240) | $1570 | ||

| 7513 | 32 (64) | 8 + IOD | 8 × 4 | 2.6 | 3.65 | 16 MiB | 144 MiB | 2P | 200 W (165-200) | $2840 | ||

| 7543(P) | 2.8 | 3.7 | 32 MiB | 272 MiB | 2P (1P) | 225 W (225-240) | $3761 ($2730) | |||||

| 75F3 | 2.95 | 4.0 | 2P | 280 W (225-280) | $4860 | |||||||

| 7573X | 8* + IOD | 2.8 | 3.6 | 96 MiB | 784 MiB | $5590 | ||||||

| 7R13[51] | 48 (96) | 6 + IOD | 6 × 8 | TBD | 3.7 | 32 MiB | 216 MiB | TBD | TBD | OEM/AWS | ||

| 7643(P) | 8 + IOD | 8 × 6 | 2.3 | 3.6 | 280 MiB | 2P (1P) | 225 W (225-240) | $4995 ($2722) | ||||

| 7663 | 56 (112) | 8 × 7 | 2.0 | 3.5 | 32 MiB | 284 MiB | 2P | 240 W (225-240) | $6366 | |||

| 7663P | 1P | 240 W (225-280) | $3139 | |||||||||

| 7713(P) | 64 (128) | 8 × 8 | 2.0 | 3.675 | 32 MiB | 288 MiB | 2P (1P) | 225 W (225-240) | $7060 ($5010) | |||

| 7763 | 2.45 | 3.4 | 2P | 280 W (225-280) | $7890 | |||||||

| 7773X | 8* + IOD | 2.2 | 3.5 | 96 MiB | 800 MiB | $8800 | ||||||

- ^ Core Complexes (CCX) × cores per CCX

Fourth generation Epyc (Genoa, Bergamo and Siena)

[edit]On November 10, 2022, AMD launched the fourth generation of Epyc server and data center processors based on the Zen 4 microarchitecture, codenamed Genoa.[52] At their launch event, AMD announced that Microsoft and Google would be some of Genoa's customers.[53] Genoa features between 16 and 96 cores with support for PCIe 5.0 and DDR5. There was also an emphasis by AMD on Genoa's energy efficiency, which according to AMD CEO Lisa Su, means "lower total cost of ownership" for enterprise and cloud datacenter clients.[54] Genoa uses AMD's new SP5 (LGA 6096) socket.[55]

On June 13, 2023, AMD introduced Genoa-X with 3D V-Cache technology for technical computing performance and Bergamo (9734, 9754 and 9754S) for cloud native computing.[56]

On September 18, 2023, AMD introduced the low power Siena lineup of processors, based on the Zen 4c microarchitecture. Siena supports up to 64 cores on the new SP6 socket, which is currently only used by Siena processors. Siena uses the same I/O die as Bergamo, however certain features, such as dual socket support, are removed, and other features are reduced, such as the change from 12 channel memory support to 6 channel memory support.[57]

In May 2024, AMD launched the Raphael lineup of processors, based on the Zen4 microarchitecture. Raphael support up to 16 cores on the AM5 socket.

| Model | Fab | Cores (Threads) |

Chiplets | Core config[i] |

Clock rate (GHz) |

Cache (MB) | Socket | Socket count |

PCIe 5.0 lanes |

Memory support |

TDP | Release date |

Price (USD) | |||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Base | Boost | L1 | L2 | L3 | DDR5 ECC | |||||||||||

| Entry Level (Zen 4 cores) | ||||||||||||||||

| 4124P | TSMC N5 |

4 (8) | ? | ? | 3.8 | 5.1 | 0.256 | 4 | 16 | AM5 | 1P | 24 | DDR5-5200 dual-channel |

65 W | May 21, 2024 | $??? |

| 4244P | 6 (12) | 3.8 | 0.384 | 6 | 32 | |||||||||||

| 4344P | 8 (16) | 3.8 | 5.3 | 0.5 | 8 | 32 | ||||||||||

| 4364P | 4.5 | 5.4 | 32 | 105 W | ||||||||||||

| 4464P | 12 (24) | 3.7 | 5.4 | 0.768 | 12 | 64 | 65 W | |||||||||

| 4484PX | 4.4 | 5.6 | 128 | 120 W | ||||||||||||

| 4564P | 16 (32) | 4.5 | 5.7 | 1 | 16 | 64 | 170 W | |||||||||

| 4584PX | 4.2 | 5.7 | 128 | 120 W | ||||||||||||

| Low Power & Edge (Zen 4c cores) | ||||||||||||||||

| 8024P | TSMC N5 |

8 (16) | 4 × CCD 1 × I/OD |

4 × 2 | 2.4 | 3.0 | 0.5 | 8 | 32 | SP6 | 1P | 96 | DDR5-4800 six-channel |

90 W | Sep 18, 2023 | $409 |

| 8024PN | 2.05 | 80 W | $525 | |||||||||||||

| 8124P | 16 (32) | 4 × 4 | 2.45 | 1 | 16 | 64 | 125 W | $639 | ||||||||

| 8124PN | 2.0 | 100 W | $790 | |||||||||||||

| 8224P | 24 (48) | 4 × 6 | 2.55 | 1.5 | 24 | 160 W | $855 | |||||||||

| 8224PN | 2.0 | 120 W | $1,015 | |||||||||||||

| 8324P | 32 (64) | 4 × 8 | 2.65 | 2 | 32 | 128 | 180 W | $1,895 | ||||||||

| 8324PN | 2.05 | 130 W | $2,125 | |||||||||||||

| 8434P | 48 (96) | 4 × 12 | 2.5 | 3.1 | 3 | 48 | 200 W | $2,700 | ||||||||

| 8434PN | 2.0 | 3.0 | 155 W | $3,150 | ||||||||||||

| 8534P | 64 (128) | 4 × 16 | 2.3 | 3.1 | 4 | 64 | 200 W | $4,950 | ||||||||

| 8534PN | 2.0 | 175 W | $5,450 | |||||||||||||

| Mainstream Enterprise (Zen 4 cores) | ||||||||||||||||

| 9124 | TSMC N5 |

16 (32) | 4 × CCD 1 × I/OD |

4 × 4 | 3.0 | 3.7 | 1 | 16 | 64 | SP5 | 1P/2P | 128 | DDR5-4800 twelve-channel |

200 W | Nov 10, 2022 | $1,083 |

| 9224 | 24 (48) | 4 × 6 | 2.5 | 3.7 | 1.5 | 24 | 200 W | $1,825 | ||||||||

| 9254 | 4 × 6 | 2.9 | 4.15 | 128 | 220 W | $2,299 | ||||||||||

| 9334 | 32 (64) | 4 × 8 | 2.7 | 3.9 | 2 | 32 | 210 W | $2,990 | ||||||||

| 9354 | 8 × CCD 1 × I/OD |

8 × 4 | 3.25 | 3.75 | 256 | 280 W | $3,420 | |||||||||

| 9354P | 1P | $2,730 | ||||||||||||||

| Performance Enterprise (Zen 4 cores) | ||||||||||||||||

| 9174F | TSMC N5 |

16 (32) | 8 × CCD 1 × I/OD |

8 × 2 | 4.1 | 4.4 | 1 | 16 | 256 | SP5 | 1P/2P | 128 | DDR5-4800 twelve-channel |

320 W | Nov 10, 2022 | $3,850 |

| 9184X | 3.55 | 4.2 | 768 | Jun 13, 2023 | $4,928 | |||||||||||

| 9274F | 24 (48) | 8 × 3 | 4.05 | 4.3 | 1.5 | 24 | 256 | Nov 10, 2022 | $3,060 | |||||||

| 9374F | 32 (64) | 8 × 4 | 3.85 | 4.3 | 2 | 32 | $4,860 | |||||||||

| 9384X | 3.1 | 3.9 | 768 | Jun 13, 2023 | $5,529 | |||||||||||

| 9474F | 48 (96) | 8 × 6 | 3.6 | 4.1 | 3 | 48 | 256 | 360 W | Nov 10, 2022 | $6,780 | ||||||

| High Performance Computing (Zen 4 cores) | ||||||||||||||||

| 9454 | TSMC N5 |

48 (96) | 8 × CCD 1 × I/OD |

8 × 6 | 2.75 | 3.8 | 3 | 48 | 256 | SP5 | 1P/2P | 128 | DDR5-4800 twelve-channel |

290 W | Nov 10, 2022 | $5,225 |

| 9454P | 1P | $4,598 | ||||||||||||||

| 9534 | 64 (128) | 8 × 8 | 2.45 | 3.7 | 4 | 64 | 1P/2P | 280 W | $8,803 | |||||||

| 9554 | 3.1 | 3.75 | 360 W | $9,087 | ||||||||||||

| 9554P | 1P | $7,104 | ||||||||||||||

| 9634 | 84 (168) | 12 × CCD 1 × I/OD |

12 × 7 | 2.25 | 3.7 | 5.25 | 84 | 384 | 1P/2P | 290 W | $10,304 | |||||

| 9654 | 96 (192) | 12 × 8 | 2.4 | 3.7 | 6 | 96 | 360 W | $11,805 | ||||||||

| 9654P | 1P | $10,625 | ||||||||||||||

| 9684X | 2.55 | 3.7 | 1152 | 1P/2P | 400 W | Jun 13, 2023 | $14,756 | |||||||||

| Cloud (Zen 4c cores) | ||||||||||||||||

| 9734 | TSMC N5 |

112 (224) | 8 × CCD 1 × I/OD |

8 × 14 | 2.2 | 3.0 | 7 | 112 | 256 | SP5 | 1P/2P | 128 | DDR5-4800 twelve-channel |

340 W | Jun 13, 2023 | $9,600 |

| 9754S | 128 (128) | 8 × 16 | 2.25 | 3.1 | 8 | 128 | 360 W | $10,200 | ||||||||

| 9754 | 128 (256) | $11,900 | ||||||||||||||

- ^ Core Complexes (CCX) × cores per CCX

Fifth generation Epyc (Turin and Turin Dense)

[edit]The fifth generation of Epyc processors were showcased by AMD at Computex 2024 on June 3. Named the Epyc 9005 series, it will come in two variants:[58]

- Zen 5 based, up to 128 cores and 256 threads, built on TSMC N4X process

- Zen 5c based, up to 192 cores and 384 threads, built on TSMC N3E process

Both variants are officially referred to under the Turin codename by AMD, although the nickname of "Turin Dense" has also been used to refer to the Zen 5c based CPUs.[59]

Turin Dense support the x2AVIC CPU feature

Both of these processor series will be socket-compatible with the SP5 socket used by Genoa and Bergamo. Epyc 9005 series were launched in 10 October 2024 at AMD's Advancing AI event 2024.[60]

| Model | Fab | Cores (Threads) |

Chiplets | Core config[i] |

Clock rate (GHz) |

Cache (MB) | Socket | Socket count |

PCIe 5.0 lanes |

Memory support |

Thermal design power (TDP) |

Release date |

Release price (USD) | |||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Base | Boost | L1 Per Core |

L2 Per Core |

L3 Shared | ||||||||||||

| Turin Dense (Zen 5c cores) | ||||||||||||||||

| 9645 | TSMC N3E |

96 (192) | 8 × CCD 1 × I/OD |

8 × 12 | 2.3 | 3.7 | 80 KB | 1 MB | 256 MB | SP5 | 1P/2P | 128

(160 in 2-socket systems) |

DDR5-6400 twelve-channel |

320 W | 10 Oct, 2024 | $11048 |

| 9745 | 128 (256) | 8 × 16 | 2.4 | 400 W | $12141 | |||||||||||

| 9825 | 144 (288) | 12 × CCD 1 × I/OD |

12 × 12 | 2.2 | 384 MB | 390 W | $13006 | |||||||||

| 9845 | 160 (320) | 10 × CCD 1 × I/OD |

10 × 16 | 2.1 | 320 MB | 390 W | $13564 | |||||||||

| 9965 | 192 (384) | 12 × CCD 1 × I/OD |

12 × 16 | 2.25 | 384 MB | 500 W | $14813 | |||||||||

| Turin (Zen 5 cores) | ||||||||||||||||

| 9015 | TSMC N4X |

8 (16) | 2 × CCD 1 × I/OD |

2 × 4 | 3.6 | 4.1 | 80 KB | 1 MB | 64 MB | SP5 | 1P/2P | 128

(160 in 2-socket systems) |

DDR5-6400 twelve-channel |

125 W | 10 Oct, 2024 | $527 |

| 9115 | 16 (32) | 2 × 8 | 2.6 | 4.1 | 125 W | $726 | ||||||||||

| 9135 | 16 (32) | 3.65 | 4.3 | 200 W | $1214 | |||||||||||

| 9175F | 16 (32) | 16 × CCD 1 × I/OD |

16 × 1 | 4.2 | 5.0 | 512 MB | 320 W | $4256 | ||||||||

| 9255 | 24 (48) | 4 × CCD 1 × I/OD |

4 × 6 | 3.25 | 4.3 | 128 MB | 200 W | $2495 | ||||||||

| 9275F | 24 (48) | 8 × CCD 1 × I/OD |

8 × 3 | 4.1 | 4.8 | 256 MB | 320 W | $3439 | ||||||||

| 9335 | 32 (64) | 4 × CCD 1 × I/OD |

4 × 8 | 3.0 | 4.4 | 128 MB | 210 W | $3178 | ||||||||

| 9355P | 32 (64) | 8 × CCD 1 × I/OD |

8 × 4 | 3.55 | 4.4 | 256 MB | 1P | 128 | 280 W | $2998 | ||||||

| 9355 | 32 (64) | 3.55 | 4.4 | 1P/2P | 128

(160 in 2-socket systems) |

280 W | $3694 | |||||||||

| 9375F | 32 (64) | 3.8 | 4.8 | 320 W | $5306 | |||||||||||

| 9365 | 36 (72) | 6 × CCD 1 × I/OD |

6 × 6 | 3.4 | 4.3 | 192 MB | 300 W | $4341 | ||||||||

| 9455P | 48 (96) | 8 × CCD 1 × I/OD |

8 × 6 | 3.15 | 4.4 | 256 MB | 1P | 128 | 300 W | $4819 | ||||||

| 9455 | 48 (96) | 3.15 | 4.4 | 1P/2P | 128

(160 in 2-socket systems) |

300 W | $5412 | |||||||||

| 9475F | 48 (96) | 3.65 | 4.8 | 400 W | $7592 | |||||||||||

| 9535 | 64 (128) | 8 × 8 | 2.4 | 4.3 | 300 W | $8992 | ||||||||||

| 9555P | 64 (128) | 3.2 | 4.4 | 1P | 128 | 360 W | $7983 | |||||||||

| 9555 | 64 (128) | 3.2 | 4.4 | 1P/2P | 128

(160 in 2-socket systems) |

360 W | $9826 | |||||||||

| 9575F | 64 (128) | 3.3 | 5.0 | 400 W | $11791 | |||||||||||

| 9565 | 72 (144) | 12 × CCD 1 × I/OD |

12 × 6 | 3.15 | 4.3 | 384 MB | 400 W | $10468 | ||||||||

| 9655P | 96 (192) | 12 × 8 | 2.5 | 4.5 | 1P | 128 | 400 W | $10811 | ||||||||

| 9655 | 96 (192) | 2.5 | 4.5 | 1P/2P | 128 (160 in 2-socket systems) | 400 W | $11852 | |||||||||

| 9755 | 128 (256) | 16 × CCD 1 × I/OD |

16 × 8 | 2.7 | 4.1 | 512 MB | 500 W | $12984 | ||||||||

- ^ Core Complexes (CCX) × cores per CCX

Embedded

[edit]First generation Epyc (Snowy Owl)

[edit]In February 2018, AMD also announced the Epyc 3000 series of embedded Zen CPUs.[61]

Common features of EPYC Embedded 3000 series CPUs:

- Socket: SP4 (31xx and 32xx models use SP4r2 package).

- All the CPUs support ECC DDR4-2666 in dual-channel mode (3201 supports only DDR4-2133), while 33xx and 34xx models support quad-channel mode.

- L1 cache: 96 KB (32 KB data + 64 KB instruction) per core.

- L2 cache: 512 KB per core.

- All the CPUs support 32 PCIe 3.0 lanes per CCD (max 64 lanes).

- Fabrication process: GlobalFoundries 14 nm.

| Model | Cores (threads) |

Clock rate (GHz) | L3 cache (total) |

TDP | Chiplets | Core config[i] |

Release date | ||

|---|---|---|---|---|---|---|---|---|---|

| Base | Boost | ||||||||

| All-core | Max | ||||||||

| 3101[62] | 4 (4) | 2.1 | 2.9 | 2.9 | 8 MB | 35 W | 1 × CCD | 1 × 4 | Feb 2018 |

| 3151[62] | 4 (8) | 2.7 | 16 MB | 45 W | 2 × 2 | ||||

| 3201[62] | 8 (8) | 1.5 | 3.1 | 3.1 | 30 W | 2 × 4 | |||

| 3251[62] | 8 (16) | 2.5 | 55 W | ||||||

| 3255[63] | 25–55 W | Dec 2018 | |||||||

| 3301[62] | 12 (12) | 2.0 | 2.15 | 3.0 | 32 MB | 65 W | 2 × CCD | 4 × 3 | Feb 2018 |

| 3351[62] | 12 (24) | 1.9 | 2.75 | 60–80 W | |||||

| 3401[62] | 16 (16) | 1.85 | 2.25 | 85 W | 4 × 4 | ||||

| 3451[62] | 16 (32) | 2.15 | 2.45 | 80–100 W | |||||

- ^ Core Complexes (CCX) × cores per CCX

Chinese variants

[edit]A variant created for the Chinese server market by Hygon Information Technology is the Hygon Dhyana system on a chip.[64][65] It is noted to be a variant of the AMD Epyc, and is so similar that "there is little to no differentiation between the chips".[64] It has been noted that there is "less than 200 lines of new kernel code" for Linux kernel support, and that the Dhyana is "mostly a re-branded Zen CPU for the Chinese server market".[65] Later benchmarks showed that certain floating point instructions are performing worse, probably to comply with US export restrictions.[66] AES and other western cryptography algorithms are replaced by Chinese variants throughout the design.[66]

References

[edit]- ^ Cutress, Ian (May 30, 2017). "Computex 2017: AMD Press Event Live Blog". AnandTech. Retrieved November 7, 2022.

- ^ Kampman, Jeff (May 16, 2017). "AMD's Naples datacenter CPUs will make an Epyc splash". Tech Report. Retrieved May 16, 2017.

- ^ Cutress, Ian (June 20, 2017). "AMD's Future in Servers: New 7000-Series CPUs Launched and EPYC Analysis". AnandTech. Retrieved July 12, 2017.

- ^ Alcorn, Paul (March 15, 2021). "Watch AMD's Epyc 7003 Milan Launch Here". Tom's Hardware. Retrieved April 5, 2022.

- ^ "AMD EPYC 7763 vs AMD EPYC 7702 [cpubenchmark.net] by PassMark Software". CPU Benchmark. Retrieved April 5, 2022.

- ^ a b "AMD EPYC 7003 "Milan-X" launches March 21st, specs and pricing leaked". VideoCardz. March 20, 2022. Retrieved March 25, 2022.

- ^ a b Cutress, Ian (November 8, 2021). "AMD Gives Details on EPYC Zen4: Genoa and Bergamo, up to 96 and 128 Cores". AnandTech. Retrieved April 5, 2022.

- ^ Mujtaba, Hassan (February 28, 2021). "AMD EPYC Genoa CPU Platform Detailed - Up To 96 Zen 4 Cores, 192 Threads, 12-Channel DDR5-5200, 128 PCIe Gen 5 Lanes, SP5 'LGA 6096' Socket". Wccftech. Retrieved April 5, 2022.

- ^ servethehome (November 8, 2021). "AMD Bergamo to hit 128 Cores and Genoa at 96 Cores". ServeTheHome. Retrieved April 5, 2022.

- ^ Mujtaba, Hassan (January 10, 2022). "Another AMD EPYC Genoa 'Zen 4' CPU Leaks Out, This Time A 16 Core Chip With 2 Active CCDs". Wccftech. Retrieved April 5, 2022.

- ^ Smith, Ryan. "AMD: EPYC "Genoa-X" CPUs With 1.1GB of L3 Cache Now Available". www.anandtech.com. Retrieved September 26, 2023.

- ^ Kennedy, Patrick (July 19, 2023). "AMD EPYC Bergamo is a Fantastically Fresh Take on Cloud Native Compute". ServeTheHome. Retrieved September 27, 2023.

- ^ Kennedy, Patrick (July 19, 2023). "AMD EPYC Bergamo is a Fantastically Fresh Take on Cloud Native Compute". ServeTheHome. Retrieved September 26, 2023.

- ^ Kennedy, Patrick (September 18, 2023). "AMD EPYC 8004 Siena Launched for Lower Power EPYC Edge". ServeTheHome. Retrieved September 26, 2023.

- ^ Cozma, George. "AMD's Turin: 5th Gen EPYC Launched". chipsandcheese.com. Retrieved October 14, 2024.

- ^ Paul Alcorn (October 10, 2024). "AMD EPYC 'Turin' 9005 Series - we benchmark 192-core Zen 5 chip with 500W TDP". Tom's Hardware. Retrieved October 14, 2024.

- ^ Cutress, Ian (May 27, 2019). "AMD Confirms Zen 4 EPYC Codename, and Elaborates on Frontier Supercomputer CPU". AnandTech. Retrieved November 7, 2022.

- ^ Bonshor, Gavin (June 9, 2022). "AMD Updated EPYC Roadmap: 5th Gen EPYC "Turin" Announced, Coming by End of 2024". AnandTech. Retrieved November 7, 2022.

- ^ btarunr (June 10, 2022). "AMD Announces the "Zen 5" Microarchitecture and EPYC "Turin" Processor on 4nm". TechPowerUp. Retrieved November 15, 2022.

- ^ Shilov, Anthon (March 14, 2023). "AMD Rolls Out EPYC Embedded 9004 CPUs: Up to 96 Cores". Tom's Hardware. Retrieved June 15, 2023.

- ^ Shilov, Anthon (September 18, 2023). "AMD Launches EPYC 8004-Series 'Siena' CPUs: Up to 64 Zen 4c Cores". Tom's Hardware. Retrieved September 18, 2023.

- ^ Cutress, Ian (March 7, 2017). "AMD Prepares 32-Core Naples CPUs for 1P and 2P Servers: Coming in Q2". AnandTech. Retrieved March 7, 2017.

- ^ Morris, John (March 13, 2018). "Inside GlobalFoundries' long road to the leading edge". ZDNet. Retrieved July 17, 2019.

- ^ a b Smith, Ryan (July 26, 2018). "AMD "Rome" EPYC CPUs to Be Fabbed By TSMC". AnandTech. Retrieved June 18, 2019.

- ^ Trader, Tiffany (March 21, 2022). "AMD Milan-X CPU with 3D V-Cache Available in Four SKUs, Up to 64-Cores". HPC Wire. Retrieved May 6, 2022.

- ^ Johnson, Renee (March 7, 2017). "AMD's Naples platform prepares to take Zen into the datacenter". Tech Report. Retrieved March 7, 2017.

- ^ a b c De Gelas, Johan; Cutress, Ian (July 11, 2017). "Sizing Up the Servers: Intel's Skylake-SP Xeon vs AMD's EPYC 7000". AnandTech. Retrieved July 11, 2017.

- ^ Sozzi, Brian (November 8, 2021). "Chipmaker AMD just scored a big deal with Meta". Yahoo! Finance. Retrieved November 10, 2022.

- ^ Kennedy, Patrick (November 22, 2022). "Gigabyte has a 48 DIMM 2P AMD EPYC Genoa GPU Server at SC22". ServeTheHome. Retrieved November 26, 2022.

- ^ a b ""Zeppelin": An SoC for Multichip Architectures". October 26, 2018. Retrieved September 27, 2024.

- ^ a b c d e f g h i j k l m n "AMD EPYC 7000 Series Processors" (PDF). AMD. January 2019. Retrieved March 25, 2023.

- ^ a b c d e f g h i j k l Cutress, Ian (June 20, 2017). "AMD's Future in Servers: New 7000-Series CPUs Launched and EPYC Analysis". AnandTech. Retrieved June 21, 2017.

- ^ a b c d Kennedy, Patrick (May 16, 2017). "AMD EPYC New Details on the Emerging Server Platform". ServeTheHome. Retrieved May 16, 2017.

- ^ "AMD EPYC 7261 - PS7261BEV8RAF". CPU-World. March 26, 2023.

- ^ Kennedy, Patrick (October 31, 2018). "AMD EPYC 7261 8 Core CPU Quietly Launched L3 Cache Monster". ServeTheHome. Retrieved March 28, 2023.

- ^ "AMD EPYC 7371 - PS7371BDVGPAF". CPU-World. March 26, 2023.

- ^ "New AMD-Powered Supercomputers Unleash Discovery and Accelerate Innovation" (Press release). AMD. November 13, 2018. Retrieved March 28, 2023.

- ^ "AMD EPYC 7571 - PS7571BDVIHAF". CPU-World. March 25, 2023.

- ^ Larabel, Michael (November 7, 2018). "A Look At The AMD EPYC Performance On The Amazon EC2 Cloud". Phoronix. Retrieved March 28, 2023.

- ^ "AMD Takes High-Performance Datacenter Computing to the Next Horizon". AMD (Press release). San Francisco, CA. November 6, 2018. Retrieved December 6, 2018.

- ^ Ung, Gordon (November 7, 2018). "What AMD's 64-core 'Rome' server CPU tells us about Ryzen 2". PCWorld. Retrieved November 11, 2018.

- ^ "2nd Gen AMD EPYC Processors Set New Standard for the Modern Datacenter with Record-Breaking Performance and Significant TCO Savings". AMD (Press release). Santa Clara, CA. August 7, 2019. Retrieved August 8, 2019.

- ^ S. Smith, Matthew (2022). "Single-Chip Processors Have Reached Their Limits". IEEE Spectrum. 59 (7): 11.

- ^ Trader, Tiffany (April 14, 2020). "AMD Launches Three New High-Frequency Epyc SKUs Aimed at Commercial HPC". www.hpcwire.com.

- ^ a b c "New 2nd Gen AMD EPYC™ Processors Redefine Performance for Database, Commercial HPC and Hyperconverged Workloads". AMD. April 14, 2020.

- ^ a b c Alcorn, Paul (October 5, 2019). "AMD dishes on Zen 3 and Zen 4 architecture, Milan and Genoa roadmap". Tom's Hardware. Retrieved October 5, 2019.

- ^ Trader, Tiffany (March 15, 2021). "AMD Launches Epyc 'Milan' with 19 SKUs for HPC, Enterprise and Hyperscale". HPC Wire. Retrieved November 10, 2022.

- ^ Sandhu, Tarinder (March 21, 2022). "A deeper look into AMD Epyc 7003 Milan-X featuring 3D V-Cache". Club386. Retrieved November 10, 2022.

- ^ Bonshor, Gavin (March 21, 2022). "AMD Releases Milan-X CPUs With 3D V-Cache: EPYC 7003 Up to 64 Cores and 768 MB L3 Cache". AnandTech. Retrieved November 10, 2022.

- ^ "AMDs Exascale-Hammer: Epyc 3 mit 804 MByte Cache, Instinct MI200 mit 47,9 TFlops". c't Magazin (in German). November 8, 2021. Retrieved November 10, 2022.

- ^ "AMD EPYC 7R13 48-Core Benchmarks". openbenchmarking.org. Retrieved November 16, 2024.

- ^ Mujtaba, Hassan (November 10, 2022). "AMD 4th Gen EPYC 9004 "Genoa Zen 4" CPUs Launched: Up To 96 Cores, 192 Threads, 384 MB L3 Cache & Crushing All Other Server Chips". Wccftech. Retrieved November 11, 2022.

- ^ Lee, Jane Lanhee; Mehta, Cahvi (November 10, 2022). "AMD launches data center CPU 'Genoa', taps Google, Microsoft as customers". Reuters. Retrieved November 11, 2022.

- ^ Burt, Jeffrey (November 10, 2022). "The Acute Role Reversal for AMD and Intel in Datacenter Compute". The Next Platform. Retrieved November 11, 2022.

- ^ Alcorn, Paul (November 10, 2022). "AMD 4th-Gen EPYC Genoa 9654, 9554, and 9374F Review: 96 Cores, Zen 4 and 5nm Disrupt the Data Center". Tom's Hardware. Retrieved November 11, 2022.

- ^ "AMD Expands 4th Gen EPYC CPU Portfolio with Leadership Processors for Cloud Native and Technical Computing Workloads". amd.com. Santa Clara, California. June 13, 2023. Retrieved June 14, 2023.

- ^ "AMD Completes 4th Gen EPYC Family with the AMD EPYC 8004 Processors, Purpose Built for Cloud Services, Intelligent Edge and Telco". amd.com. Santa Clara, California. June 13, 2023. Retrieved September 18, 2023.

- ^ Alcorn, Paul (June 3, 2024). "AMD announces 3nm EPYC Turin with 192 cores and 384 threads — 5.4X faster than Intel Xeon in AI work, launches second half of 2024". Tom's Hardware. Retrieved June 17, 2024.

- ^ "AMD EPYC Turin CPUs have been pictured, up to 128 Zen5 or 192 Zen5c cores". VideoCardz.com. December 17, 2023. Retrieved June 17, 2024.

- ^ "AAMD Launches 5th Gen AMD EPYC CPUs, Maintaining Leadership Performance and Features for the Modern Data Center". ir.amd.com. October 10, 2024. Retrieved October 10, 2024.

- ^ Alcorn, Paul (February 21, 2018). "AMD Launches Ryzen Embedded V1000, EPYC Embedded 3000 Processors". Tom's Hardware. Retrieved April 5, 2018.

- ^ a b c d e f g h "Product Brief: AMD EPYC Embedded 3000 Family" (PDF). AMD. 2018. Retrieved March 26, 2023.

- ^ "AMD EPYC Embedded 3255 - PE3255BGR88AF". CPU-World. March 26, 2023.

- ^ a b Alcorn, Paul (July 6, 2018). "China Finds Zen: Begins Production Of x86 Processors Based On AMD's IP". Tom's Hardware. Retrieved July 9, 2018.

- ^ a b Larabel, Michael (June 9, 2018). "Hygon Dhyana: Chinese x86 Server CPUs Based On AMD Zen". Phoronix. Retrieved July 9, 2018.

- ^ a b Cutress, Ian; Wilson, Wendell (February 27, 2020). "Testing a Chinese x86 CPU: A Deep Dive into Zen-based Hygon Dhyana Processors". AnandTech. Retrieved September 29, 2020.