WD16

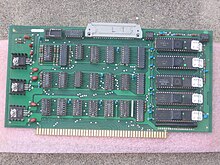

WD16 microprocessor in five 40-pin packages installed on an Alpha Microsystems AM-100 CPU board which connects to a S-100 bus. | |

| General information | |

|---|---|

| Launched | 1976 |

| Common manufacturer | |

| Performance | |

| Max. CPU clock rate | to 3.3 MHz |

| Data width | 16 |

| Address width | 16 |

| Architecture and classification | |

| Instruction set | PDP-11 like |

| Number of instructions | 119 |

| Physical specifications | |

| Package |

|

| History | |

| Successor | none |

The WD16 is a 16-bit microprocessor introduced by Western Digital in October 1976. It is based on the MCP-1600 chipset, a general-purpose design that was also used to implement the DEC LSI-11 low-end minicomputer and the Pascal MicroEngine processor. The three systems differed primarily in their microcode, giving each system a unique instruction set architecture (ISA).

The WD16 implements an extension of the PDP-11 instruction set architecture but is not machine code compatible with the PDP-11.[1] The instruction set and microcoding were created by Dick Wilcox and Rich Notari.[2] The WD16 is an example of orthogonal CISC architecture. Most two-operand instructions can operate memory-to-memory with any addressing mode and some instructions can result in up to ten memory accesses.

The WD16 is implemented in five 40-pin DIP packages. Maximum clock speed is 3.3 MHz. Its interface to memory is via a 16-bit multiplexed data/address bus.[3]

The WD16 is best known for its use in Alpha Microsystems' AM-100 and AM-100/T processor boards.[4] A prototype was demonstrated in 1977.[5] As of 1981 there were at least 5,000 Alpha Micro computers based on the WD16.[6] As late as 1982, WD16-based Alpha Micros were still being characterized as "supermicros."[7] The WD16 was superseded by the Motorola 68000 in June 1982.[8]

Memory

[edit]Data formats

[edit]The smallest unit of addressable and writable memory is the 8-bit byte. Bytes can also be held in the lower half of registers R0 through R5.[9]

16-bit words are stored little-endian with least significant bytes at the lower address. Words are always aligned to even memory addresses. Words can be held in registers R0 through R7.

32-bit double words can only be stored in register pairs with the lower word being stored in the lower-numbered register. 32 bit values are used by MUL, DIV and some rotate and arithmetic shift instructions.

Floating point values are 48 bits long and can only be stored in memory. This format is half-way between single and double precision floating point formats. They are stored an unusual middle-endian format sometimes referred to as "PDP-endian." Floating point values are always aligned to even addresses. The first word contains the sign, exponent, and high byte of the mantissa. The next higher address contains the middle two bytes of the mantissa, and the next higher address contains the lowest two bytes of the mantissa. The complete format is as follows:

1. A 1 bit sign for the entire number which is zero for positive.

2. An 8-bit base-two exponent in excess-128 notation with a range of +127, -128. The only legal number with an exponent of -128 is true zero (all zeros).

3. A 40 bit mantissa with the MSB implied.

| 15 | 14 | 7 | 6 | 0 | ||||||||||||

| Addr+0 | S | Exponent | Mantissa (high) | |||||||||||||

| 15 | 8 | 7 | 0 | |||||||||||||

| Addr+2 | Mantissa | (middle) | ||||||||||||||

| 15 | 8 | 7 | 0 | |||||||||||||

| Addr+4 | Mantissa | (low) | ||||||||||||||

Memory management

[edit]The WD16's 16-bit addresses can directly access 64 KB of memory. The WD16 does not offer any inherent memory management or protection. In the AM-100 application, the last 256 memory locations are mapped to port space.[10] As most AM-100 computers were used as multi-user computers, the memory would usually be expanded past 64K with bank switching. Although the AM-100 could be configured for up to 22 users and 512 Kilobytes of RAM,[6] a typical memory configuration for a 9-user AM-100 might be in the range of 352 Kilobytes.[11] In 1981 an optional AM-700 memory management unit was offered for the AM-100/T which allowed memory segmentation in 256 byte increments.[12]

CPU registers

[edit]

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

The CPU contains eight general-purpose 16-bit registers, R0 to R7. The registers can be used for any purpose with these exceptions: Register R7 is the program counter (PC). Although any register can be used as a stack pointer, R6 is the stack pointer (SP) used for hardware interrupts and traps. R0 is the count for the block transfer instructions.[9]

Addressing modes

[edit]Most instructions allocate six bits to specify each operand. Three bits select one of eight addressing modes and three bits select a general register. The encoding of the six bit operand addressing mode is as follows:[9]

| 5 | 3 | 2 | 0 | ||

| Mode | Register | ||||

In the following sections, each item includes an example of how the operand would be written in assembly language. Rn means one of the eight registers, written R0 through R7.

General register addressing modes

[edit]The following eight modes can be applied to any general register. Their effects when applied to R6 (the stack pointer, SP) and R7 (the program counter, PC) are set out separately in the following sections.

| Code | Name | Example | Description |

|---|---|---|---|

| 0n | Register | Rn | The operand is in Rn |

| 1n | Register deferred | (Rn) | Rn contains the address of the operand |

| 2n | Autoincrement | (Rn)+ | Rn contains the address of the operand, then increment Rn |

| 3n | Autoincrement deferred | @(Rn)+ | Rn contains the address of the address of the operand, then increment Rn by 2 |

| 4n | Autodecrement | −(Rn) | Decrement Rn, then use the result as the address of the operand |

| 5n | Autodecrement deferred | @−(Rn) | Decrement Rn by 2, then use the result as the address of the address of the operand |

| 6n | Index | X(Rn) | Rn+X is the address of the operand |

| 7n | Index deferred | @X(Rn) | Rn+X is the address of the address of the operand |

In index and index deferred modes, X is a 16-bit value taken from a second word of the instruction. In double-operand instructions, both operands can use these modes. Such instructions are three words long.

Autoincrement and autodecrement operations on a register are by 1 in byte instructions, by 2 in word instructions, and by 2 whenever a deferred mode is used, since the quantity the register addresses is a (word) pointer.

Program counter addressing modes

[edit]When R7 (the program counter) is specified, four of the addressing modes naturally yield useful effects:

| Code | Name | Example | Description |

|---|---|---|---|

| 27 | Immediate | #n | The operand is the next word of the instruction |

| 37 | Absolute | @#a | The address of the operand is the next word of the instruction |

| 67 | Relative | a | The address of the operand is the next word of the instruction added to the PC |

| 77 | Relative deferred | @a | The address of the address of the operand is the next word of the instruction added to PC |

There are only two common uses of absolute mode, whose syntax combines immediate and deferred mode. The first is accessing the reserved processor locations at 0000-003F. The other is to specify input/output registers in port space, as the registers for each device have specific memory addresses. Relative mode has a simpler syntax and is more typical for referring to program variables and jump destinations. A program that uses relative mode (and relative deferred mode) exclusively for internal references is position-independent; it contains no assumptions about its own location, so it can be loaded into an arbitrary memory location, or even moved, with no need for its addresses to be adjusted to reflect its location. In computing such addresses relative to the current location, the processor performs relocation on the fly.

Immediate and absolute modes are merely autoincrement and autoincrement deferred mode, respectively, applied to PC. When the auxiliary word is in the instruction, the PC for the next instruction is automatically incremented past the auxiliary word. As PC always points to words, the autoincrement operation is always by a stride of 2.

Stack addressing modes

[edit]R6, also written SP, is used as a hardware stack for traps and interrupts. A convention enforced by the set of addressing modes the WD16 provides is that a stack grows downward—toward lower addresses—as items are pushed onto it. When a mode is applied to SP, or to any register the programmer elects to use as a software stack, the addressing modes have the following effects:

| Code | Name | Example | Description |

|---|---|---|---|

| 16 | Deferred | (SP) | The operand is on the top of the stack |

| 26 | Autoincrement | (SP)+ | The operand is on the top of the stack, then pop it off |

| 36 | Autoincrement deferred | @(SP)+ | A pointer to the operand is on top of stack; pop the pointer off |

| 46 | Autodecrement | −(SP) | Push a value onto the stack |

| 66 | Indexed | X(SP) | The operand is located X distance from the top of stack |

| 76 | Indexed deferred | @X(SP) | The pointer to the operand is located X distance from the top of stack |

Although software stacks can contain bytes, SP always points to a stack of words. Autoincrement and autodecrement operations on SP are always by a stride of 2.

Instruction set

[edit]Most of the WD16 instructions operate on bytes and words. Bytes are specified by a register number—identifying the register's low-order byte—or by a memory location. Words are specified by a register number or by the memory location of the low-order byte, which must be an even number. All opcodes and addresses are expressed in hexadecimal.[9]

Double-operand instructions

[edit]The high-order four bits specify the operation to be performed. Two groups of six bits specify the source operand addressing mode and the destination operand addressing mode, as defined above. This group of instructions takes up 75% of available opcodes.

| 15 | 12 | 11 | 9 | 8 | 6 | 5 | 3 | 2 | 0 | ||||||

| Opcode | Src | Register | Dest | Register | |||||||||||

| Opcode | Mnemonic | Operation |

|---|---|---|

| 1000 | ADD | Add: Dest ← Dest + Src

|

| 2000 | SUB | Subtract: Dest ← Dest - Src

|

| 3000 | AND | And: Dest ← Dest ∧ Src

|

| 4000 | BIC | Bit clear: Dest ← Dest ∧ (-1 - Src)

|

| 5000 | BIS | Bit Set: Dest ← Dest ∨ Src

|

| 6000 | XOR | Exclusive or: Dest ← Dest ⊻ Src

|

| 9000 | CMP | Compare: Set-flags(Src − Dest)

|

| A000 | BIT | Bit test: Set-flags(Dest ∧ Src)

|

| B000 | MOV | Move: Dest ← Src

|

| C000 | CMPB | Compare byte: Set-flags(Src − Dest)

|

| D000 | MOVB | Move byte: Dest ← Src (Register destination sign-extends into bits 8-15)

|

| E000 | BISB | Bit set byte: Dest ← Dest ∨ Src

|

Some two-operand instructions utilize an addressing mode for one operand and a register for the second operand:

| 15 | 9 | 8 | 6 | 5 | 3 | 2 | 0 | ||||||||

| Opcode | Reg | Src/Dest | Register | ||||||||||||

The high-order seven bits specify the operation to be performed, six bits specify the operand addressing mode and three bits specify a register or register pair. Where a register pair is used (written below as "Reg+1:Reg") Reg contains the low-order portion of the operand. The next higher numbered register contains the high-order portion of the operand (or the remainder).

| Opcode | Mnemonic | Operation |

|---|---|---|

| 7200 | LEA | Load effective address: Reg ← ea(Dest)

|

| 73C0 | JMP | Jump: PC ← ea(Dest) (This is the same as LEA PC,Dest and shares the same opcode.)

|

| 7400 | ASH | Arithmetic shift: if Src < 0 then Reg ← Shift-right(Reg, -Src) else Reg ← Shift-left(Reg, Src)

|

| 7800 | XCH | Exchange: Reg ↔ Src

|

| 7A00 | ASHC | Arithmetic shift combined (32 bit): if Src < 0 then (Reg+1:Reg) ← Shift-right((Reg+1:Reg), -Src) else (Reg+1:Reg) ← Shift-left((Reg+1:Reg), Src)

|

| 7C00 | MUL | Multiply: (Reg+1:Reg) ← Reg × Src

|

| 7E00 | DIV | Divide: Compute (Reg+1:Reg) ÷ Src; Reg ← quotient; Reg+1 ← remainder

|

Single-operand instructions

[edit]The high-order ten bits specify the operation to be performed, with bit 15 generally selecting byte versus word addressing. A single group of six bits specifies the operand as defined above.

| 15 | 6 | 5 | 3 | 2 | 0 | ||||||||||

| Opcode | Src/Dest | Register | |||||||||||||

| Opcode | Mnemonic | Operation |

|---|---|---|

| 0BC0 | SWAB | Swap bytes of word: Dest ← (Dest × 256) ∨ (Dest ÷ 256)

|

| 8BC0 | SWAD | Swap digits of byte: Dest ← (Dest × 16) ∨ (Dest ÷ 16)

|

| 0840 | CLR | Clear: Dest ← 0

|

| 8840 | CLRB | |

| 0C00 | COM | Complement: Dest ← (-1 - Dest)

|

| 8C00 | COMB | |

| 0C80 | INC | Increment: Dest ← Dest + 1

|

| 8C80 | INCB | |

| 0CC0 | DEC | Decrement: Dest ← Dest − 1

|

| 8CC0 | DECB | |

| 0C40 | NEG | Negate: Dest ← -Dest

|

| 8C40 | NEGB | |

| 0B00 | SET | Set: Dest ← -1

|

| 8B00 | SETB | |

| 0A80 | TST | Test: Set-flags(Src)

|

| 8A80 | TSTB | |

| 0A00 | ROR | Rotate right: Dest:Cflag ← Rotate-right(Dest:Cflag, 1)

|

| 8A00 | RORB | |

| 0A40 | ROL | Rotate left: Cflag:Dest ← Rotate-left(Cflag:Dest, 1)

|

| 8A40 | ROLB | |

| 0B80 | ASR | Arithmetic shift right: Dest ← Dest ÷ 2, sign preserved

|

| 8B80 | ASRB | |

| 0AC0 | ASL | Arithmetic shift left: Dest ← Dest × 2

|

| 8AC0 | ASLB | |

| 8D80 | ADC | Add carry: Dest ← Dest + Cflag

|

| 8DC0 | SBC | Subtract carry: Dest ← Dest - Cflag

|

| 0D00 | IW2 | Increment word by 2: Dest ← Dest + 2

|

| 0DC0 | TJMP | Tabled jump: PC ← PC + (Dest), PC ← PC + @PC

|

| 0D80 | TCALL | Tabled call: -(SP) ← PC, PC ← PC + (Dest), PC ← PC + @PC

|

| 0D40 | SXT | Sign extend: if N flag = 1 then Dest ← -1 else Dest ← 0

|

| 8D00 | LSTS | Load processor status: PSW ← Dest

|

| 8D40 | SSTS | Save processor status: Dest ← PSW

|

Single-operand short immediate instructions

[edit]The high-order seven bits and bits 5 and 4 specify the operation to be performed. A single group of three bits specifies the register. A four bit count field contains a small immediate or a count. In all cases one is added to this field making the range 1 through 16.

| 15 | 9 | 8 | 6 | 5 | 4 | 3 | 0 | ||||||||

| Opcode | Reg | Op | Count | ||||||||||||

| Opcode | Mnemonic | Operation |

|---|---|---|

| 0800 | ADDI | Add immediate: Reg ← Reg + Count + 1

|

| 0810 | SUBI | Subtract immediate: Reg ← Reg - Count - 1

|

| 0820 | BICI | Bit clear immediate: Reg ← Reg ∧ (-1 - (Count+1))

|

| 0830 | MOVI | Move immediate: Reg ← Count + 1

|

| 8800 | SSRR | Right rotate multiple: Reg:C-flag ← Rotate-right(Reg:C-flag, Count+1)

|

| 8810 | SSLR | Left rotate multiple: C-flag:Reg ← Rotate-left(C-flag:Reg, Count+1)

|

| 8820 | SSRA | Right arithmetic shift multiple: Reg:C-flag ← Arithmetic-shift-right(Reg, Count+1)

|

| 8830 | SSLA | Left arithmetic shift multiple: C-flag:Reg ← Arithmetic-shift-left(Reg, Count+1)

|

| 8E00 | SDRR | Double right rotate multiple (33 bit): Reg+1:Reg:C-flag ← Rotate-right(Reg+1:Reg:C-flag, Count+1)

|

| 8E10 | SDLR | Double left rotate multiple (33 bit): C-flag:Reg+1:Reg ← Rotate-left(C-flag:Reg+1:Reg, Count+1)

|

| 8E20 | SDRA | Double right arithmetic shift multiple (32 bit): Reg:Reg+1:C-flag ← Arithmetic-shift-right(Reg:Reg+1, Count+1)

|

| 8E30 | SDLA | Double left arithmetic shift multiple (32 bit): C-flag:Reg:Reg+1 ← Arithmetic-shift-left(Reg:Reg+1, Count+1)

|

Floating point instructions

[edit]The high-order eight bits specify the operation to be performed. Two groups of four bits specify the source and destination addressing mode and register. If field I = 0, designated register contains the address of the operand, the equivalent of addressing mode (Rn). If field I = 1, designated register contains the address of the address of the operand, the equivalent of addressing mode @0(Rn).

| 15 | 8 | 7 | 6 | 4 | 3 | 2 | 0 | ||||||||

| Opcode | I | SReg | I | DReg | |||||||||||

| Opcode | Mnemonic | Operation |

|---|---|---|

| F000 | FADD | Floating add: Dest ← Dest + Src

|

| F100 | FSUB | Floating subtract: Dest ← Dest - Src

|

| F200 | FMUL | Floating Multiply: Dest ← Dest × Src

|

| F300 | FDIV | Floating Divide: Dest ← Dest ÷ Src

|

| F400 | FCMP | Floating Compare: Dest - Src

|

Opcodes F500 to FFFF were mapped to a fourth microm to implement eleven more floating point instructions. There is no evidence that this fourth microm was ever produced. When a standard WD16 processor executes opcodes F500 to FFFF, the reserved opcode trap is taken, loading PC from 001A.

Block transfer instructions

[edit]The high-order ten bits specify the operation to be performed. Two groups of three bits specify the source and destination registers. In all cases the source register contains the address of the first word or byte of memory to be moved, and the destination register contains the address of the first word or byte of memory to receive the data being moved. The number of words or bytes being moved is contained in R0 as a unsigned integer. The count ranges from 1–65536. These instructions are fully interruptible.

| 15 | 6 | 5 | 3 | 2 | 0 | ||||||||||

| Opcode | SReg | DReg | |||||||||||||

| Opcode | Mnemonic | Operation |

|---|---|---|

| 0E00 | MBWU | Move block of words up: (DReg) ← (SReg), SReg ← SReg + 2, DReg ← DReg + 2, R0 ← R0 - 1, until R0 = 0

|

| 0E40 | MBWD | Move block of words down: (DReg) ← (SReg), SReg ← SReg - 2, DReg ← DReg - 2, R0 ← R0 - 1, until R0 = 0

|

| 0E80 | MBBU | Move block of bytes up: (DReg) ← (SReg), SReg ← SReg + 1, DReg ← DReg + 1, R0 ← R0 - 1, until R0 = 0

|

| 0EC0 | MBBD | Move block of bytes down: (DReg) ← (SReg), SReg ← SReg - 1, DReg ← DReg - 1, R0 ← R0 - 1, until R0 = 0

|

| 0F00 | MBWA | Move block of words to address: (DReg) ← (SReg), SReg ← SReg + 2, R0 ← R0 - 1, until R0 = 0

|

| 0F40 | MBBA | Move block of bytes to address: (DReg) ← (SReg), SReg ← SReg + 1, R0 ← R0 - 1, until R0 = 0

|

| 0F80 | MABW | Move address to block of words: (DReg) ← (SReg), DReg ← DReg + 2, R0 ← R0 - 1, until R0 = 0

|

| 0FC0 | MABB | Move address to block of bytes: (DReg) ← (SReg), DReg ← DReg + 1, R0 ← R0 - 1, until R0 = 0

|

Branch instructions

[edit]The high-order byte of the instruction specifies the operation. The low-order byte is a signed word offset relative to the current location of the program counter. This allows for forward and reverse branches in code. Maximum branch range is +128, -127 words from the branch op code.

In most branch instructions, whether the branch is taken is based on the state of the condition codes. A branch instruction is typically preceded by a two-operand CMP (compare) or BIT (bit test) or a one-operand TST (test) instruction. Arithmetic and logic instructions also set the condition codes. In contrast to Intel processors in the x86 architecture, MOV instructions set them too, so a branch instruction could be used to branch depending on whether the value moved was zero or negative.

| 15 | 8 | 7 | 0 | ||||||||||||

| Opcode | Offset | ||||||||||||||

| Opcode | Mnemonic | Condition or Operation |

|---|---|---|

| 0100 | BR | Branch always PC ← PC + (2 × Sign-extend(Offset))

|

| 0200 | BNE | Branch if not equal Z = 0

|

| 0300 | BEQ | Branch if equal Z = 1

|

| 0400 | BGE | Branch if greater than or equal (N ⊻ V) = 0

|

| 0500 | BLT | Branch if less than (N ⊻ V) = 1

|

| 0600 | BGT | Branch if greater than (Z ∨ (N ⊻ V)) = 0

|

| 0700 | BLE | Branch if less than or equal (Z ∨ (N ⊻ V)) = 1

|

| 8000 | BPL | Branch if plus N = 0

|

| 8100 | BMI | Branch if minus N = 1

|

| 8200 | BHI | Branch if higher (C ∨ Z) = 0

|

| 8300 | BLOS | Branch if lower or same (C ∨ Z) = 1

|

| 8400 | BVC | Branch if overflow clear V = 0

|

| 8500 | BVS | Branch if overflow set V = 1

|

| 8600 | BCC or BHIS | Branch if carry clear, or Branch if higher or same C = 0

|

| 8700 | BCS or BLO | Branch if carry set, or Branch if lower C = 1

|

The limited range of the branch instructions meant that as code grows, the target addresses of some branches may become unreachable. The programmer would change the one-word Bcc to the two-word JMP instruction. As JMP has no conditional forms, the programmer would change the Bcc to its opposite sense to branch around the JMP.

| 15 | 9 | 8 | 6 | 5 | 0 | ||||||||||

| Opcode | Reg | Offset | |||||||||||||

| Opcode | Mnemonic | Operation |

|---|---|---|

| 7600 | SOB | Subtract One and Branch: Reg ← Reg - 1; if Reg ≠ 0 then PC ← PC - (2 × Offset)

|

SOB (Subtract One and Branch) is another conditional branch instruction. The specified register is decremented by 1 and if the result is not zero, a reverse branch is taken based on the 6-bit word offset.

Subroutine instructions

[edit]| 15 | 9 | 8 | 6 | 5 | 3 | 2 | 0 | ||||||||

| Opcode | Reg | Src | Register | ||||||||||||

| Opcode | Mnemonic | Operation |

|---|---|---|

| 7000 | JSR | Jump to subroutine: -(SP) ← Reg; Reg ← PC; PC ← Src

|

JSR calls a subroutine. A group of six bits specifies the addressing mode. The JSR instruction can save any register on the stack. Programs that do not need this feature specify PC as the register (JSR PC, address) and the subroutine returns using RTN PC. If a routine were called with, for example JSR R4, address, then the old value of R4 would be saved on the top of the stack and the return address (just after JSR) would be in R4. This lets the routine gain access to values coded in-line by specifying (R4)+ or to in-line pointers by specifying @(R4)+. The autoincrementation moves past these data, to the point at which the caller's code resumes. Such a routine would specify RTN R4 to return to its caller.

The JSR PC,@(SP)+ form can be used to implement coroutines. Initially, the entry address of the coroutine is placed on the stack and from that point the JSR PC,@(SP)+ instruction is used for both the call and the return statements. The result of this JSR instruction is to exchange the contents of the PC and the top element of the stack, and so permit the two routines to swap control and resume operation where each was terminated by the previous swap.

| 15 | 3 | 2 | 0 | ||||||||||||

| Opcode | Reg | ||||||||||||||

| Opcode | Mnemonic | Operation |

|---|---|---|

| 0018 | RTN | Return from subroutine: PC ← Reg; Reg ← (SP)+

|

| 0028 | PRTN | Pop stack and return: SP ← SP + (2 × @SP), PC ← Reg; Reg ← (SP)+

|

PRTN deletes a number of parameters from the stack and returns. PRTN is the WD16's answer to the PDP-11's convoluted MARK instruction. Unlike MARK, PRTN executes in program space and can use any register as a linkage register. For this explanation, R5 will be used as the linkage. First, the caller pushes R5 on the stack. Next, any number of word arguments may be placed on the stack. The caller then puts the number of argument words + 1 into R5. The caller executes a JSR R5,address instruction which pushes the number of argument words + 1 onto the stack, places the return address in R5, and jumps to the subroutine. After executing its code, the subroutine terminates with a PRTN R5. PRTN doubles the number on the top of stack and adds it to SP, deleting the parameters. PRTN then continues by returning to caller with the equivalent of an RTN R5, loading R5 into PC and popping R5.

Single register instructions

[edit]These instructions have a 13 bit opcode and a three bit register argument.

| 15 | 3 | 2 | 0 | ||||||||||||

| Opcode | Reg | ||||||||||||||

| Opcode | Mnemonic | Operation |

|---|---|---|

| 0010 | IAK | Interrupt acknowledge: Interrupt acknowledge state code, Reg ← Bus read

|

| 0020 | MSKO | Mask out: (002E) ← Reg, Mask out state code

|

Implied parameter instructions

[edit]| 15 | 0 | ||||||||||||||

| Opcode | |||||||||||||||

| Opcode | Mnemonic | Operation |

|---|---|---|

| 0000 | NOP | No operation: Do nothing

|

| 0001 | RESET | Reset: Transmit reset pulse to I/O devices

|

| 0002 | IEN | Interrupt enable: I2 ← 1

|

| 0003 | IDS | Interrupt disable: I2 ← 0

|

| 0004 | HALT | Halt: Executes the selected halt option

|

| 0005 | XCT | Execute single instruction: PC ← (SP)+, PS ← (SP)+, set trace flag, execute opcode, -(SP) ← PS, -(SP) ← PC, trace flag reset, If no error PC ← (0020) else PC ← (001E)

|

| 0006 | BPT | Breakpoint trap:-(SP) ← PS, -(SP) ← PC, PC ← (002C)

|

| 0007 | WFI | Wait for interrupt: Enable interrupts (I2 ← 1). Bus activity ceases.

|

| 0008 | RSVC | Return from supervisor call (B or C): REST, SP ← SP + 2, RTT

|

| 0009 | RRTT | Restore and return from trap: REST, RTT

|

| 000A | SAVE | Save registers: -(SP) ← R5, -(SP) ← R4, -(SP) ← R3, -(SP) ← R2, -(SP) ← R1, -(SP) ← R0

|

| 000B | SAVS | Save status: SAVE, -(SP) ← (002E), (002E) ← (002E) ∨ Mask, MSKO, IEN. Note Mask is stored in the second word of instruction.

|

| 000C | REST | Restore registers: R0 ← (SP)+, R1 ← (SP)+, R2 ← (SP)+, R3 ← (SP)+, R4 ← (SP)+, R5 ← (SP)+

|

| 000D | RRTN | Restore and return: REST, PC ← (SP)+

|

| 000E | RSTS | Restore status: (002E) ← (SP)+, MSKO, REST, RTT

|

| 000F | RTT | Return from trap: PC ← (SP)+, PS ← (SP)+

|

Supervisor calls

[edit]These instructions are used to implement operating system (supervisor) calls. All have a six bit register argument. SVCB and SVCC are designed so an argument to the operating system can use most of the addressing modes supported by the native instruction set.

| 15 | 6 | 5 | 0 | ||||||||||||

| Opcode | Arg | ||||||||||||||

| Opcode | Mnemonic | Operation |

|---|---|---|

| 0040 | SVCA | Supervisor Call A: -(SP) ← PS ,-(SP) ← PC, PC ← (0022) + Arg × 2, PC ← (PC)

|

| 0080 | SVCB | Supervisor Call B: TMPA ← SP, -(SP) ← PS, -(SP) ← PC, TMPB ← SP, -(SP) ← TMPA, -(SP) ← R5, -(SP) ← R4, -(SP) ← R3, -(SP) ← R2, -(SP) ← R1, -(SP) ← R0, R1 ← TMPB, R5 ← Arg × 2, PC ← (0024)

|

| 00C0 | SVCC | Supervisor Call C: TMPA ← SP, -(SP) ← PS, -(SP) ← PC, TMPB ← SP, -(SP) ← TMPA, -(SP) ← R5, -(SP) ← R4, -(SP) ← R3, -(SP) ← R2, -(SP) ← R1, -(SP) ← R0, R1 ← TMPB, R5 ← Arg × 2, PC ← (0026)

|

Condition-code operations

[edit]| 15 | 4 | 3 | 2 | 1 | 0 | ||||||||||

| Opcode | N | Z | V | C | |||||||||||

| Opcode | Mnemonic | Operation |

|---|---|---|

| 0030 | LCC | Load condition codes: Load according to N, Z, V, C bits

|

The four condition codes in the processor status word (PSW) are

- N indicating a negative value

- Z indicating a zero (equal) condition

- V indicating an overflow condition, and

- C indicating a carry condition.

Interrupts

[edit]WD16 has three types of interrupts: non-vectored, vectored, and halt. Non-vectored and vectored interrupts are enabled and disabled by the IEN and IDS instructions. Halt cannot be disabled.

A non-vectored interrupt (NVI) has priority over vectored interrupts. The NVI is used for only two things: power fail and line clock. (A line clock is typically a 50 or 60 Hz input used for time slicing and time keeping.) When a NVI is received, PS and PC are pushed. Power fail status is checked. If it is a power fail, the WD16 will jump to the address stored at 0014. If not a power fail, then a line clock tick is assumed and the WD16 will jump to the address stored at 002A.

Sixteen interrupt vectors are supported. When a vectored interrupt is received, PS and PC are pushed. During interrupt acknowledge, the WD16 accepts a four-bit interrupt number provided by the interrupting device. The interrupt vector table address is fetched from 0028 and the interrupt number is added to it, pointing to one of 16 words in the table. A word offset is fetched from the table and added to its own table address. The result is loaded into PC causing a jump to the interrupt service routine. What simultaneous interrupts are taken is determined by a 16-bit interrupt priority mask that is mostly implemented with external hardware. The WD16 stores the current priority mask at 002E while transmitting the mask directly to hardware. The mask is manipulated with the MSKO, SAVS, and RSTS instructions.

Halt is a non-maskable interrupt that can be used for a programmer's switch or other uses depending on how its jumpers are configured. Although halt can alter the execution address and is not masked by interrupt enable, it cannot be used a typical non-maskable interrupt because PC is not pushed. Depending on jumpers, the halt line may not even halt. If the HALT instruction is executed, it may be cleared by the halt line, again, depending on jumpers.

Reserved low-memory locations

[edit]Memory locations between 0000 and 003F have fixed functions defined by the processor. All addresses below are word addresses.[9]

| Vector | Condition |

|---|---|

| 0000-0010 | R0 - R5, SP, PC, and PS for power up/halt options |

| 0012 | bus error PC |

| 0014 | nonvectored interrupt power fail PC |

| 0016 | power up/halt option power restore PC |

| 0018 | parity error PC |

| 001A | reserved op code PC |

| 001C | illegal op code format PC |

| 001E | XCT error PC |

| 0020 | XCT trace PC |

| 0022 | SVCA table address |

| 0024 | SVCB PC |

| 0026 | SVCC PC |

| 0028 | vectored interrupt (I0) table address |

| 002A | nonvectored interrupt (I1) PC |

| 002C | BPT PC |

| 002E | I/O priority interrupt mask |

| 0030-003C | Floating point scratchpad |

| 003E | Floating point error PC |

Performance

[edit]WD16 processor speed varies by clock speed, memory configuration, op code, and addressing modes. Instruction timing has up to three components, fetch/execute of the instruction itself and access time for the source and the destination. The last two components depend on the addressing mode. For example, at 3.3 MHz, an instruction of the form ADD x(Rm),y(Rn) has a fetch/execute time of 3.3 microseconds plus source time of 2.7 microseconds and destination time of 3.0 microseconds, for a total instruction time of 9.0 microseconds. The register-to-register ADD Rm,Rn executes in 3.3 microseconds. Floating point is significantly slower. A single-and-a-half precision (48 bit) floating add instruction typically ranges from 54 to 126 microseconds. The WD16's precision is a compromise between traditional single and double precision floats.[9]

For contrast, the fastest PDP-11 computer at the time was the PDP-11/70. An instruction of the form ADD x(Rm),y(Rn) has a fetch/execute time of 1.35 microseconds plus source and destination times of 0.6 microseconds each, for a total instruction time of 2.55 microseconds. Any case where addressed memory was not in the cache adds 1.02 microseconds. The register-to-register ADD Rm,Rn could execute from the cache in 0.3 microseconds.[13] A single-precision floating add instruction executed by the FP11-C co-processor could range from 0.9 to 2.5 microseconds plus time to fetch the operands which could range up to 4.2 microseconds.[14]

The WD16 block transfer instructions approximately double the speed of moves and block I/O. A word moved with MOV (R1)+,(R2)+, SOB R0,loop instructions takes 9.6 microseconds per iteration. The MBWU R1,R2 equivalent takes 4.8 microseconds per iteration.

The Association of Computer Users performed a series of benchmarks on an AM-100T-based system costing $35,680 (equivalent to $131,941 in 2023). They found that their CPU-bound benchmark executed in 31.4 seconds on the AM-100T compared to 218 seconds for the average single user system in the $15,000 to $25,000 price range.[15] In a group of multi-user computers priced between $25,000 and $50,000, the AM-100T was in the "upper third" for speed.[16]

The Creative Computing Benchmark of May 1984 placed the WD16 (in the AM-100T application) as number 34 out of 183 machines tested. The elapsed time was 10 seconds, compared to 24 seconds for the IBM PC.[17]

Emulator

[edit]Virtual Alpha Micro is an open source WD16 emulator. Written in C, it emulates the WD16 processor and the Alpha Micro AM-100 hardware environment. The author claims it runs on Linux (including Raspberry Pi), Windows, and Macintosh desktops, though no binaries are provided. It will run the Alpha Micro Operating System (AMOS) and all associated programs. In 2002, Alpha Micro granted limited permission to distribute AMOS 4.x or 5.0 binaries including the manuals for hobby use only.[18]

See also

[edit]References

[edit]- ^ Flystra, Daniel (April 1977). "New Hobbyist System Supports Timesharing" (PDF). Byte. 2 (4): 142–144. Retrieved 21 November 2022.

- ^ Wilcox, Dick (January 1977). "A PDP-11-Like 16-Bit Micro for the S-100 Bus". Dr. Dobbs's Journal of Computer Calisthenics and Orthodontia. 2 (1): 3–7. Retrieved 14 June 2022.

- ^ MCP-1600 Microprocessor Users Manual (PDF). Western Digital. 1975. Retrieved 28 April 2022.

- ^ Stan, Viet (May 1983). "The Battle of the Disk Operating Systems" (PDF). Computers & Electronics. 21 (5): 19. Retrieved 8 June 2023.

- ^ Craig, John (April 1977). "Around the Industry" (PDF). Kilobaud: The Small Computer Magazine (4): 10. Retrieved 23 November 2022.

- ^ a b Kee, Hank (August 1981). "Alpha Micro System Revisited" (PDF). Microsystems. 2 (4): 26. Retrieved 1 March 2022.

- ^ Fox, Tom (January 1982). "Business Systems for '82". Interface Age. 7 (1): 75. Retrieved 3 November 2022.

- ^ "Alpha Microsystems makes record sales". InfoWorld. 4 (44): 11. November 8, 1982. Retrieved 3 November 2022.

- ^ a b c d e f "WD16 Microcomputer Programmer's Reference Manual" (PDF). Western Digital. Retrieved 10 December 2021.

- ^ "Technical Manual for AM-100" (PDF). Alpha Microsystems. Retrieved 19 December 2021.

- ^ "Alpha Micro AM100". Obsolete Computer Museum. Retrieved 19 December 2021.

- ^ Memory Management with the Memory Partition Controller (PDF) (A01 ed.). Alpha Micro. October 1981. pp. 139–155. Retrieved 14 June 2022.

- ^ PDP-11/70 Processor Handbook (PDF). DEC. 1976. Appendix C, Instruction Timing.

- ^ DEC PDP-11 Processor Handbook, 1975, Pages 379-391, FP11-C Instruction Timing

- ^ "Alpha Micro AM-100T". Association of Computer Users Benchmark Report. 3.2 (6): 9. November 1980. Retrieved 3 November 2022.

- ^ "12 Issue Summary". Association of Computer Users: Benchmark Report. 3.2 (14): 4. June 1982. Retrieved 3 November 2022.

- ^ Ahl, David H. (May 1984). "Creative Computing Benchmark". Creative Computing Magazine. 10 (5): 6. Retrieved 2 November 2022.

- ^ Noel, Mike. "VAM Virtual Alpha Micro". Retrieved 13 July 2022.