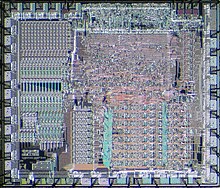

Signetics 2650

Signetics 2650AN | |

| General information | |

|---|---|

| Launched | 1975 |

| Common manufacturer | |

| Performance | |

| Max. CPU clock rate | 1.2 MHz |

| Data width | 8 |

| Address width | 15 |

| Physical specifications | |

| Package |

|

The Signetics 2650 was an 8-bit microprocessor introduced in July 1975.[1] According to Adam Osborne's book An Introduction to Microprocessors Vol 2: Some Real Products, it was "the most minicomputer-like" of the microprocessors available at the time. A combination of missing features and odd memory access limited its appeal, and the system saw little use in the market.

Development

[edit]

In 1972, Signetics' Jack Curtis[a] hired John Kessler of IBM to lead the design of a new single-chip CPU intended to compete with minicomputer systems. Kessler selected the IBM 1130 as the model for the new design. The 1130, released in 1965, was a 16-bit minicomputer that shared many design features with other minis of the era.[2]

While Kessler designed the architecture, Kent Andreas laid out the CPU using a recently developed ion implantation NMOS process. In contrast to the far more common PMOS process of the era, NMOS used less power and dissipated less heat. This allowed the chip to be run at higher speeds than PMOS CPU designs, and the first 2650's ran at the same 1.25 MHz speed as the contemporary models of the 1130.[2]

When it was designed in 1972, the 2650 was among the most advanced designs on the market, easily outperforming and out-featuring the Intel 4004 and 8008 of the same era. Despite this, the design was not released to production. At the time, Signetics was heavily involved with Dolby Laboratories, developing integrated circuits that implemented Dolby's suite of noise-reduction systems. Production of the 2650 was pushed back, and the CPU was not formally introduced until July 1975. By 1975, several new CPUs had been introduced, designed from the start to be 8-bit machines rather than mimicking an older design, and the 2650's advantages were no longer as compelling.[2]

In 1975, Philips purchased Signetics, and from that point versions of the 2650 can be found with both Signetics or Philips branding.[2]

In March 1976, Signetics reached a second-source agreement with Advanced Memory Systems (AMS). At that time, most CPU firms were very small and no one would buy a design from a company that might go bankrupt. Second-sourcing was an important guarantee that the design would remain available in this eventuality. AMS was already acting as a second-source for the RCA 1802, an advanced CMOS design, and the NMOS 2650 was seen as a useful adjunct that would not directly compete with the 1802. Unfortunately, in November AMS was purchased by Intersil, who had their own Intersil 6100, a single-chip version of the PDP-8 mini. Intersil dropped production of the 2650.[2]

Signetics tried again with National Semiconductor in 1977, who planned to introduce versions in the last quarter of the year. For unknown reasons, this appears to have never happened, and only a single example of an NS version, from France, has ever been found.[2]

Signetics continued the development of the 2650, introducing two new models in 1977. The 2650A was a reworked version of the original layout intended to improve yield, and thus reduce cost. Speed remained unchanged at 1.25 MHz for the base model and 2 MHz for the -1 versions. The 2650B was based on the A, added two new instructions, and improved the performance of a number of existing instructions.[2]

Description

[edit]

| 14 | 13 | 12 | 11 | 10 | 09 | 08 | 07 | 06 | 05 | 04 | 03 | 02 | 01 | 00 | (bit position) |

| Main general purpose registers | |||||||||||||||

| REG0 | |||||||||||||||

| REG1 | |||||||||||||||

| REG2 | |||||||||||||||

| REG3 | |||||||||||||||

| Alternate general purpose registers | |||||||||||||||

| REG1' | |||||||||||||||

| REG2' | |||||||||||||||

| REG3' | |||||||||||||||

| Instruction Address register | |||||||||||||||

| Page | |||||||||||||||

| Subroutine return address stack | |||||||||||||||

| S0 | |||||||||||||||

| S1 | |||||||||||||||

| S2 | |||||||||||||||

| S2 | |||||||||||||||

| S4 | |||||||||||||||

| S5 | |||||||||||||||

| S6 | |||||||||||||||

| S7 | |||||||||||||||

| Program Status Words | |||||||||||||||

| S | F | II | Stack Ptr | PSU | |||||||||||

| CC | ID | RS | WC | OV | CM | C | PSL | ||||||||

The overall design of the 2650 was based on the IBM 1130. As such, the 2650 has a number of features that were common on 1960s minicomputers, but rarely found on newly designed microprocessors of the 1970s. Among these, for instance, were status bits that were used to track the status of input/output devices, which makes it simpler to write interfacing code.[2] Another mini-like feature was its use of vectored interrupts, which allowed devices to call the correct interrupt handler code by putting its memory location on the data bus and then forcing an interrupt. This avoids the need to write a centralized interrupt handler that reads additional data from the bus, determines which device driver is being invoked and then calls it; the 2650 can jump directly to the correct code, potentially stored on the device itself.

The 2650's processor registers were divided into sets, with a single global register R0 used as the accumulator, and two sets of three index registers, both named R1, R2 and R3, for a total of seven registers.[3] For clarity, the second set was sometimes referred to as R1', R2' and R3' ("prime"). At any one time, one of the two sets of indexes were visible to the CPU. Which set was visible was controlled by a bit in the status register, PSW. One could easily switch between the two sets of registers with a single instruction.[4] This allowed rapid switching of values during subroutine calls, operating system switches, or handling interrupts. Unlike the 1130, the registers were only 8-bit wide rather than 16-bit, but there were two sets in the 2650 rather than one in the 1130.[2]

Another of its mini-like features was the extensive support for indirect addressing on most instructions. Many instructions require data to be read from a location in memory, in most CPUs of the era that would be a single byte of data that is stored in memory referred to by a 16-bit location. In the 2650, the high-bit of that 16-bit location indicated indirection, meaning that the data was not located at this location in memory, but the one encoded in the remaining 15 bits of the address.[4] This style of access allowed blocks of data to be more easily accessed than in systems that provided indirection solely through special instructions or index registers. One could step through memory by incrementing the address value stored in that single location in memory. This also resulted in considerable numbers of math instructions being applied to addresses, and to improve the performance of these operations, the 2650 included a second arithmetic logic unit just for address calculations.[3]

The downside to this approach was that the high-bit was no longer part of the address, meaning the address space was only 15 bits, and the machine could access only a total of 32 KB of memory. The address space was further limited by the use of another two bits of the address to indicate the indexing mode for all logical and arithmetic (i.e. non-branch) instructions. These bits controlled functions like whether the address should be post-incremented or pre-decremented, which is extremely useful for constructing loops. But with all of these bits already accounted for, only 13 were available for addresses in these instructions, meaning only 8 KB could be addressed directly. This meant the main memory was broken up as four 8 KB blocks.[3] To access memory outside the 8 KB where the instruction was located, the data bytes being pointed to had to contain an indirect address, pointing to some other location in memory.[4] Doing so forced another memory read cycle, slowing performance.

When the 2650 was designed in 1972, these limitations on address space were not significant due to the small size and high cost of the static RAM memory typically used with these processors. At the time, machines typically contained 2 or 4 KB of RAM. But with the increasing use of dynamic RAM from the mid-1970s, machines with 8 and 16 KB of RAM, and ultimately 64 KB, became common and the addressing system on the 2650 became a significant hindrance.

The 2650 also contained an on-die call stack, rather than the more common solution that sets aside a location in memory to hold the stack. The stack pointer was held in three bits in the PSW. An on-die stack is much faster, as the data can be accessed directly without waiting for it to be read from external memory, but it also takes up room on the die and is always limited in size as a result of practical tradeoffs. In the 2650, the return address stack was eight 15-bit entries deep.[3] This allowed programs to nest subroutines to eight levels.

While there were nine different addressing modes, the lack of 16-bit registers and the 13–15-bit address space prevented widespread use. Despite this, an operating system ("2650 DOS")[5] was available, along with 8 KB and 12 KB BASIC interpreters (sold by Central Data Corporation USA), and many games of the Hunt the Wumpus style. Most programs were written in assembly language.

Uses

[edit]

Signetics sold 2650-based microprocessor development boards, first the PC1001[6][7] and then its successor, the PC1500 "Adaptable Board Computer", ranging in price from A$165 to A$400. The chip by itself sold for around A$20. Several hardware construction projects and programming articles were published in magazines such as Electronics Australia and Elektor and related kits were sold by electronics stores. These factors led to its use by a number of hobbyists in many countries such as Australia, U.S.A.,[8] United Kingdom, the Netherlands[9] and Germany.[10]

Two types of video game console used the Signetics 2650 or 2650A. The first group of consoles are based on the Signetics 2636 video display controller; the 1292 Advanced Programmable Video System and the closely related Interton Video Computer 4000 belong to this group. Those were released in Germany in 1976 and 1978 respectively. The second group of consoles were based on the Signetics 2637 as a video display controller; Emerson Arcadia 2001 which was released in 1982 and which used a Signetics 2650 running at 0.895 MHz as a CPU belong to this group together with many other ones software-compatible (Leonardo, Hanimex MPT-03 etc.).[11]

At least six coin-operated video games were released in the 1970s which used the 2650 CPU: Atari, Inc. Quiz Show, Meadows Games 3D Bowling, Meadows Games Gypsy Juggler, Meadows Games Lazer Command, Cinematronics Embargo, and a 1978 clone of Space Invaders by Zaccaria called The Invaders (the original by Taito uses an Intel 8080 CPU).

Italian game manufacturer Zaccaria released 28 pinball machines based on the 2650 CPU. Their successor company, MrGame, released four additional pinball machines using the 2650. Zaccaria seems to have licensed its design to Technoplay as well, and several more pinball machines were released using variations of Zaccaria's circuit board designs.

At least two coin-operated video games were released in the 1980s using the 2650. Hunchback, and Hunchback Olympic.

The processor was also used in the Signetics Instructor 50, which was a small computer designed to teach the use and programming of the Signetics 2650 CPU.

The 2650 was also used in some large items of equipment such as the Tektronix 8540, a microprocessor software development system which supported various in-circuit emulator, trace memory and logic analyser cards for real-time debugging of microprocessor systems, as practiced in the 1980s. The 2650 provided the base operating system functions, data transfer, and interface to a host computer or serial computer terminal.

The processor was most suited as a microcontroller, due to its extensive I/O support:

- Single bit i/o pins on the processor (sense/flag bits)

- Signals to directly address two 8-bit I/O ports (control and data ports) using single byte instructions (port i/o). This circumvented the elaborate hardware other systems needed for memory-mapped I/O

- Signals to address another 256 I/O ports using an 8-bit address and two byte instructions, again, limiting the amount of hardware (address decoding) required. Philips emphasized this use as a micro-controller with a demonstration program showing the 2650 controlling an intelligent elevator system. Also, at trade fairs they showed the 2650 controlling a miniature 'sort and stack' robot

Industrial Microcomputer System – IMS

[edit]

For a short time starting 1979, Philips sold a modular 2650 computer called the 'IMS' – Industrial Microcomputer System,[12] based on the Eurocard format in a 19" rack. It included CPU, PROM, RAM, input, output and teletype modules. This system was meant as a more intelligent programmable logic controller. For development, they later added DEBUG, DISPLAY, INTERRUPT and MODEST ((E)PROM programmer) modules.

Architecture

[edit]The 2650 was supplied in a 40 pin plastic or ceramic DIL enclosure. An external single phase clock signal and a single 5V supply were needed.

The 2650 had many unusual features when compared to other microprocessors of the time:

- It was a fully static NMOS 8-bit microprocessor. The static nature was unusual for the time, and meant that the processor could be halted simply by stopping the clock signal. Programmers made grateful use of this feature to "single step' through a program using a push-button switch to generate the clock pulses.

- Unique was the 8-level 15-bit wide stack for the subroutine and interrupt return addresses which was integrated into the processor. The stack pointer used 3 bits of the upper status register. This meant subroutines and interrupts could only be nested 8 levels deep.

- The processor had only 13 real address lines, a further 2 address lines were connected to a 2-bit 'page register', resulting in a 32 KB address space. The page register was set when an absolute (direct) branch instruction, which used a full 15-bit address, was executed. All logical and arithmetic instructions used a 13-bit address augmented by the contents of the page register, thereby limiting their scope to an 8 KB page. These 2 upper address lines were also used (multiplexed) to select the appropriate I/O port during I/O operations (Control port, Data port or Extended port).

- Although the 2650 had only one interrupt input, this was a 'vectored' interrupt – the interrupting device needed to put a zero-relative displacement on the data bus, that would be used as the operand of a ZBSR (zero branch to subroutine relative) instruction to branch to the specified interrupt routine. Therefore, using indirect addressing, a maximum of 30 interrupt vectors could be stored in the first 64 bytes of memory. (The first three bytes were needed to hold an unconditional branch to the 'reset' routine). This vectored interrupt is also reminiscent of the PDP-11 minicomputer.

Instruction set

[edit]Although the 2650 is basically an 8-bit microprocessor, 64 opcodes are actually 9-bit, and another 32 opcodes are 11-bit (using bits in the address field). Of the remaining 128 8-bit opcodes, 124 (126 in the 2650B) are implemented, giving a total of 444 (446) instructions.

Many more instructions are available as the behavior of the standard instructions can be modified by setting or clearing status bits: WC (with or without carry) and COM (logical or arithmetic compare). This doubled the number of rotate, add, subtract and compare instructions.

The instruction set is strongly orthogonal: all logic and arithmetic instructions can use all nine addressing modes:

- register

- immediate

- PC relative and PC relative indirect

- absolute and absolute indirect

- absolute indexed, absolute indexed with auto-increment, and absolute indexed with auto-decrement, both direct and indirect

The most significant bit of all relative and absolute addresses is used to indicate indirection.

The only exceptions are where the opcodes of meaningless operations are used for other purposes:

- the opcode for AND register zero with register zero is used for the HALT instruction.

- the opcode for STORE register zero into register zero is used for the NOP instruction.

Although the instruction LOAD register zero with register zero would appear meaningless, and was officially unsupported, it did set the condition code and was often used to determine the status of this register.[citation needed]. The Signetics Assembler generated code as if it was the instruction IORZ,R0 instead.

Indexing

[edit]With all arithmetic and logical instructions using absolute (direct) addressing, bits 14 and 13 of the address field are used to indicate the indexing mode as follows:

- 00 no indexing

- 01 indexing with auto increment

- 10 indexing with auto decrement

- 11 indexing only

When indexing is specified, the register defined in the instruction becomes the index register, and the source/destination is implicitly Register zero. For indirect indexing, Post indexing is used, i.e. the indirect address is first fetched from memory and then the index is added to it.

Branching

[edit]Probably the most mini-computer like aspect of the 2650 is the enormous number (62) of branch (jump) instructions; all these instructions could also use indirection:

- BIRR and BIRA: Increment register and branch if non-zero (R0, R1, R2 or R3) with relative or absolute addressing

- BDRR and BDRA: Decrement register and branch if non-zero (R0, R1, R2 or R3) with relative or absolute addressing

- BRNR and BRNA: branch if register non-zero (R0, R1, R2 or R3) with relative or absolute addressing

- BCTR and BCTA: branch on condition True (zero, greater-than, less-than or unconditional) with relative or absolute addressing

- BCFR and BCFA: branch on condition False (zero, greater-than or less-than) with relative or absolute addressing.

- ZBRR: branch relative to address zero

- BXA: branch indexed

Like the Intel 8080, the 2650 had instructions to conditionally branch to, and return from, a subroutine:

- BSTR and BSTA: branch to subroutine on condition True (zero, greater-than, less-than or unconditional) with relative or absolute addressing

- BSFR and BSFA: branch to subroutine on condition False (zero, greater-than or less-than) with relative or absolute addressing

- BSNR and BSNA: branch to subroutine if register non-zero (R0, R1, R2 or R3) with relative or absolute addressing

- RETC: return from subroutine on condition True (zero, greater-than, less-than or unconditional)

- RETE: return from interrupt on condition True (zero, greater-than, less-than or unconditional)

- ZBSR: branch to subroutine relative to address zero

- BSXA: branch to subroutine indexed

Only the branch instructions using absolute addressing used all 15 bits of the address field as address. Using such a branch instruction was, therefore, the only way to set the two bits in the page register (controlling bits 14 and 13 of the address bus) and changing the current 8 KB page.

Versions

[edit]- 2650 original version with 1.25 MHz maximum clock frequency

- 2650A improved version (minor fabrication changes to improve stability) 1.25 MHz maximum clock frequency

- 2650A-1 as 2650A with 2 MHz maximum clock frequency

- 2650B

- 2650B-1 as 2650B with 2 MHz maximum clock frequency

The 2650B had the following changes and improvements over the 2650A:[13]

- Two new signals – "Bus Enable" on pin 15 and "Cycle Last" on pin 25.

- Program Status Word Upper bits 3 and 4 are settable and testable user flags (unused on the 2650A).

- Two new instructions STPL and LDPL to save and restore the lower status register from memory in order to simplify interrupt processing.

- Single byte register R0 instructions execute faster (one cycle rather than two).

Second sources

[edit]

In 1975, Signetics was sold to Philips and the 2650 was later incorporated into the Philips Semiconductors line. They made a version of the 2650 called the MAB2650A. Valvo, a subsidiary of Philips, sold the 2650 in Germany. Valvo also sold the VA200 single board (Eurocard) 2650 computer with 4 KB PROM/EPROM, 1 KB RAM and four I/O ports.[14]

Other producers of licensed copies of the chip were Harris and Intersil.

Peripheral chips

[edit]The 2650 came with a full complement of peripheral chips:

- 2621 Video Encoder (PAL)

- 2622 Video Encoder (NTSC)

- 2636 Programmable Video Interface

- 2637 Universal Video Interface

- 2651 Programmable Communication Interface

- 2652 Multi-Protocol Communications Circuit (incl. Synchronous Data Link Control (SDLC))

- 2653 Polynomial Generator / Checker

- 2655 Programmable Peripheral Interface

- 2656 SMI (System memory interface)

- 2657 Direct Memory Access

- 2661 Enhanced Programmable Communication Interface (EPCI)

- 2670 Display Character and Graphics Generator

- 2671 Programmable Keyboard and Communications Controller

- 2672 Programmable Video Timing Controller

- 2673 Video Attributes Controller

Many of these peripheral chips were designed so they could also be used with other microprocessors, for example the datasheet of the 2672 suggests using it with an Intel 8048 microcontroller.

Philips Technical Note 083 describes how to interface the 2651 PCI to various other microprocessors, such as the 8080, 8085, Z80, 8048 and 6800

Descendants of the 2651/2661 serial communications chips are still sold as the Philips SC26 series.

The 2656 was specifically designed to augment, and interface with, the 2650 and make a 2-chip computer possible. It contained everything the 2650 lacked to make a complete computer:

- 2 KB 8-bit mask-programmed ROM program memory

- 128 bytes 8-bit RAM memory

- Clock generator with crystal or RC network

- Power-on reset

- Eight general purpose I/O pins

The I/O pins could be used as an 8-bit I/O port or programmed to generate enable signals for extra RAM, ROM or I/O ports. This was achieved by mask-programming a Programmable Logic Array in the 2656.

To develop and test the design before committing it to production, Philips sold the PC4000, a 2656 emulator board using PROMs and FPLAs to emulate the ROM and PLA in the 2656.

Notes

[edit]- ^ Best known for his joke article on write-only memory.

References

[edit]Citations

[edit]- ^ "Microcomputer Digest Vol. 2 No. 1 July 1975" (PDF). Archived (PDF) from the original on 1 February 2014. Retrieved 1 February 2014.

- ^ a b c d e f g h i "Signetics 2650: An IBM on a Chip". CPU Shack. 16 October 2016.

- ^ a b c d Rowe 1976.

- ^ a b c "Signetics 2650 family". CPU World. 11 February 2014.

- ^ 2650 DOS

- ^ Signetics Technical Note SP50; 2650 evaluation printed circuit board level system PC1001

- ^ Signetics Technical Note SS50; PC1001 monitor program "PIPBUG"

- ^ Build a 2650 Microcomputer system, Radio Electronics magazine: April, May, June 1977

- ^ Hobby Computer Club (HCC) 2650 user group

- ^ Programmierbeispiele mit dem Mikroprozessor 2650, Johann Hatzenbichler, 1978 OCLC 74475572

- ^ Sharke, Ward; et al. (4 June 2002). "Arcadia 2001: Frequently Asked Questions". See "Credits and contributions" section for authors. Retrieved 26 December 2023.

- ^ Industrial Microcomputer System; System Specification, Philips Electronic Components and materials, 1980

- ^ Philips 2650 Series microprocessor short-form manual 02-1979; 9398 209 50011

- ^ VALVO VA 200 Mikrocomputer im Europa-Format: VALVO Applikationslaboratorium März 1978

- ^ 2650PC-4000 memory interface emulator using PROM's and FPLA's

Bibliography

[edit]- Rowe, Jamieson (September 1976). "The Signetics 2650" (PDF). Electronics Australia.

External links

[edit]- 2650 Emulators

- Datasheet

- Signetics 2650 family CPU World

- Instructor 50 Old-computers.com

- Adaptable Board Computer development system complete with 1 KiB PipBug monitor and 512 bytes of RAM

- the 2650 at www.cpu-museum.com (archived)

- Electronics Australia 2650 board at yesterdaystechnology.com

- Signetics 2650: An IBM on a Chip retrospective at The CPUSHACK Museum (October 16, 2016)

- Zaccaria The Invaders at Museum of the Game

- A 2650 cross assembler is available from https://shop-pdp.net/index.php