SGI Challenge

This article needs additional citations for verification. (October 2019) |

| Developer | Silicon Graphics |

|---|---|

| Type | Server, supercomputer |

| Release date | 1992 |

| CPU | MIPS R4400, MIPS R8000, MIPS R10000 |

| Memory | 64 MB–128 GB |

| Successor | Origin 200 and Origin 2000 |

The Challenge, code-named Eveready (deskside models) and Terminator (rackmount models), is a family of server computers and supercomputers developed and manufactured by Silicon Graphics in the early to mid-1990s that succeeded the earlier Power Series systems (not to be confused with IBM Power Systems). The Challenge was later succeeded by the NUMAlink-based Origin 200 and Origin 2000 in 1996.

Models

[edit]There are three distinctive models of the Challenge. The first model, simply known as the "Challenge" used the 64-bit R4400. With the introduction of the R8000, the Challenge was upgraded to support more processors and memory as well as featuring support for this new processor. Such systems are known as the "POWER Challenge". During the final years of the Challenge architecture's useful life, the line was upgraded to support R10000 microprocessors. Older Challenge systems using the R10000 were known as the "Challenge 10000", while the newer POWER Challenge systems using the R10000 were known as the "POWER Challenge 10000".

Models suffixed with "GR" (for "Graphics Ready") could support the RealityEngine and InfiniteReality graphics subsystems. Standard models were either servers or supercomputers with no graphics support.

Challenge

[edit]| Model | # of CPUs | CPU | CPU MHz | L2 cache | Memory | Enclosure | Introduced | Discontinued |

|---|---|---|---|---|---|---|---|---|

| DM (Departmental) |

1, 2 or 4 | R4400 | 100, 150, 200 or 250 |

1 MB | ? | Deskside | 1994 | ? |

| L (Large) |

1 to 12 | R4400 | 100, 150, 200 250 |

1 or 4 MB | Up to 2 GB | Deskside | 1993 | ? |

| GR (Graphics Ready) |

2, 4, 8, 12, 16 or 24 | R4400 | 100, 150, 200 250 |

1 or 4 MB | ? | Rackmount | ? | ? |

| XL (Extra Large) |

2, 4, 8, 12, 16, 24 or 36 | R4400 | 100, 150, 200 or 250 | 1 or 4 MB | 16 GB | Rackmount | 1993 | ? |

Challenge 10000

[edit]| Model | # of CPUs | CPU | CPU MHz | L2 cache | Memory | Chassis | Introduced | Discontinued |

|---|---|---|---|---|---|---|---|---|

| L (Large) |

1 to 12 | R10000 | 195 | 1 or 2 MB | Up to 2 GB | Deskside | ? | ? |

| GR (Graphics Ready) |

2, 4, 8, 12, 16 or 24 | R10000 | 195 | 1 or 2 MB | ? | Rackmount | ? | ? |

| XL (Extra Large) |

2, 4, 8, 12, 16, 24 or 36 | R10000 | 195 | 1 or 2 MB | 16 GB | Rackmount | ? | ? |

POWER Challenge

[edit]

The POWER Challenge was announced on 28 January 1993[1] and was intended to compete against supercomputer companies such as Cray Research.[1] At the time of its announcement, Silicon Graphics claimed that the POWER Challenge would have the same level of performance as Cray's Cray Y-MP with a single microprocessor.[1] The new model was introduced in the middle of 1994 and used the MIPS R8000 microprocessor chip set, which consisted of the R8000 microprocessor and R8010 floating point unit accompanied by a "streaming" cache and its associated controllers. Much of the POWER Challenge's performance depended on the R8000, a microprocessor intended to achieve supercomputing performance and designed for floating-point scientific applications.[2] As a result, the R8000 had features such as fused multiply–add instructions and a large cache.[2]

In 1995, Silicon Graphics upgraded the POWER Challenge with R8000 microprocessors clocked at 90 MHz, enabling the system to scale up to 6.48 GFLOPS, an improvement of 1 GFLOPS over the previous R8000 microprocessor clocked at 75 MHz.

| Model | # of CPUs | CPU | CPU MHz | L2 cache | Memory | Chassis | Introduced | Discontinued |

|---|---|---|---|---|---|---|---|---|

| L (Large) |

1 to 6 | R8000 | 75 or 90 | 4 MB | Up to 6 GB | Deskside | ? | 21 January 1997 |

| GR (Graphics Ready) |

1 to 12 | R8000 | 75 or 90 | 4 MB | ? | Rackmount | ? | 21 January 1997 |

| XL (Extra Large) |

2 to 18 | R8000 | 75 or 90 | 4 MB | 64 MB to 16 GB | Rackmount | ? | 21 January 1997 |

POWER Challenge 10000

[edit]

The POWER Challenge 10000 referred to POWER Challenge-based systems that used the R10000 microprocessor. These models were introduced in January 1996, succeeding the R4400-based Challenge and the R8000-based POWER Challenge, although such systems co-existed with the POWER Challenge 10000 for some time. To support the new R10000s, a new CPU board, the "IP25" was introduced. The new CPU board, like the previous IP19 CPU board, supports one, two, or four processors and their associated secondary caches.

| Model | # of CPUs | CPU | CPU MHz | L2 cache | Memory | Chassis |

|---|---|---|---|---|---|---|

| L (Large) |

1 to 12 | R10000 | 195 | 1 or 2 MB | Up to 6 GB | Deskside |

| XL (Extra Large) |

2, 4, 8, 12, 16, 24 or 36 |

R10000 | 195 | 1 or 2 MB | 64 MB to 16 GB | Rackmount |

CHALLENGEarray

[edit]The CHALLENGEarray and POWER CHALLENGEarray is a cluster of Challenge or POWER Challenge servers respectively. The CHALLENGEarray supports 2 to 288 R10000 processors while the POWER CHALLENGEarray supports 2 to 144 R8000 processors and up to 128 GB of memory. The POWER CHALLENGEarray was introduced on 15 November 1994.

Other models

[edit]Other systems from Silicon Graphics that used the "Challenge" brand were the Challenge M and the Challenge S. These systems were repackaged Silicon Graphics Indigo2 and Indy workstations that were not configured with the graphics hardware that made them useful as workstations. These systems were Challenges in name only and have no architectural similarity with the multiprocessing Challenges, although they had cases with the same blue hue as proper Challenges. They were branded as such in order for the systems to be marketed as part of the Challenge server family, positioned as entry level servers.

Description

[edit]The deskside enclosure is predominately black with a vertical blue strip on right side. The rackmount enclosure is black, but the front is blue with a horizontal black strip in the middle where the system controller display is mounted. Deskside systems have a width of 54 cm (21 inches), a height of 65 cm (26 inches), a depth of 74 cm (29 inches) and a weighs a minimum of 89 kg (195 lbs).[3] Rackmount systems have a width of 69 cm (27 inches), a height of 159 cm (62.3 inches), a depth of 122 cm (48 inches) and weighs a maximum of 544 kg (1200 lbs).[4]

Rackmount systems have a 1,900 watt power supply.

Architecture

[edit]The Challenge is a shared-memory multiprocessor computer. The system is based on nodes, which are implemented as boards that plug into a midplane containing Ebus slots and the POWERpath-2 "Ebus" bus, a system bus that the nodes use to communicate with other nodes. The POWERpath-2 bus consists of a 256-bit path for data and a 40-bit path for addressing clocked at 47.6 MHz (21-nanosecond cycle), providing 1.2 GB/s of sustained bandwidth.

The midplane in DM and L models contains five Ebus slots that can support a combination of three CPU, one memory or two POWERchannel-2 interface boards. The midplane also contains five VME expansion slots.

The midplane in XL models contains fifteen Ebus slots that can support a combination of nine CPU, eight memory or five POWERchannel-2 interface boards. The midplane also contains six VME expansion slots and three power board slots.

Boards

[edit]The Challenge uses a board set known as the POWERpath-2 board set, code named "Everest". The boards that make up this board set are the IP19, IP21, IP25 CPU boards, the MC3 memory board and the IO4 POWERchannel-2 interface board.

CPU boards

[edit]The CPU board contains the microprocessors. There are three models of CPU boards: the IP19, IP21 and IP25. The IP19 can be configured with two or four R4400 microprocessors. It also contains five CPU Interface ASICs, four for implementing the data path and one for implementing the address path. These ASICs contain an average of 80,000 gates each.[5] The IP21 supports the R8000 microprocessor and can be configured with one or two such microprocessors. The IP25 supports one, two, or four R10000 microprocessors.

MC3

[edit]Memory is provided by the MC3 memory board, which contains thirty-two single in-line memory module (SIMM) slots and two leaf controllers. Fast page mode (FPM) error correcting code (ECC) SIMMs with capacities of 16 MB (known as the "high-density" SIMM) and 64 MB (known as the "super-density" SIMM) are supported, enables the board to provide 64 MB to 2 GB of memory. The SIMMs are installed in groups of four.

The memory is organized into eight banks, with four banks forming a leaf. The memory can be interleaved if there are two or more leaves present in the system. The memory bus is 576-bit wide, with a 512-bit path for data and a 64-bit path for ECC. The memory is controlled by the two leaf controllers. Each leaf controller manages four banks of memory and half of a memory transaction. It is therefore connected to 256 bits of the memory bus and 128 bits of the POWERpath-2 bus.[6]

Memory transactions are 128-byte wide, the same width as the cache line of the MIPS microprocessors used. A memory read is completed in two cycles of the memory clock, and is buffered by the leaf controllers before it is placed in a sent over the POWERpath-2 bus in four cycles of the POWERpath-2 bus clock.[6]

The SIMMs are protected by ECC, and the ECC implementation can correct single-bit errors and detect double-bit errors. The SIMMs also contain built-in self-test circuitry, which tests the SIMM during power on or reset and alerts the firmware, which disables the bank(s) of memory containing faulty SIMM(s), if faults are detected.[6]

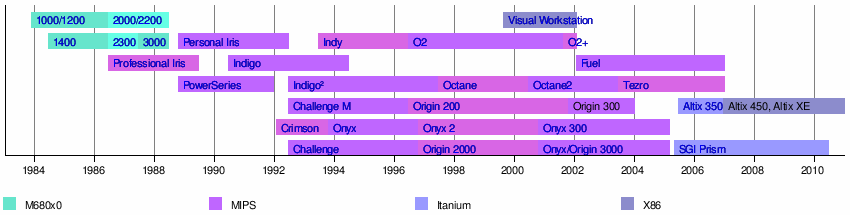

SGI timeline

[edit]

References

[edit]- ^ a b c "New 'Micros' Disclosed". The New York Times, 28 January 1993.

- ^ a b Peter Yan-Tek Hsu. "Design of the R8000 Microprocessor". IEEE Micro, April 1994.

- ^ * M. Schwenden. Deskside POWER CHALLENGE and CHALLENGE L Owner’s Guide, 23 April 1996, document number: 007-1732-060. Silicon Graphics, Inc. Archived 3 March 2016 at the Wayback Machine

- ^ "Greg Morris and Pablo Rozal. POWER CHALLENGE and CHALLENGE XL Rackmount Owner's Guide, 23 April 1996, document number: 007-1735-050. Silicon Graphics, Inc" (PDF). Archived from the original (PDF) on 3 March 2016. Retrieved 28 August 2008.

- ^ Mike Galles and Eric Williams. "Performance optimizations, implementation, and verification of the SGI Challenge multiprocessor".

- ^ a b c POWER CHALLENGE Technical Report. Silicon Graphics, Inc.