Multiplexer

In electronics, a multiplexer (or mux; spelled sometimes as multiplexor), also known as a data selector, is a device that selects between several analog or digital input signals and forwards the selected input to a single output line.[1] The selection is directed by a separate set of digital inputs known as select lines. A multiplexer of inputs has select lines, which are used to select which input line to send to the output.[2]

A multiplexer makes it possible for several input signals to share one device or resource, for example, one analog-to-digital converter or one communications transmission medium, instead of having one device per input signal. Multiplexers can also be used to implement Boolean functions of multiple variables.

Conversely, a demultiplexer (or demux) is a device taking a single input and selecting signals of the output of the compatible mux, which is connected to the single input, and a shared selection line. A multiplexer is often used with a complementary demultiplexer on the receiving end.[1]

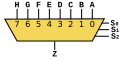

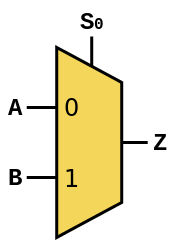

An electronic multiplexer can be considered as a multiple-input, single-output switch, and a demultiplexer as a single-input, multiple-output switch.[3] The schematic symbol for a multiplexer is an isosceles trapezoid with the longer parallel side containing the input pins and the short parallel side containing the output pin.[4] The schematic on the right shows a 2-to-1 multiplexer on the left and an equivalent switch on the right. The wire connects the desired input to the output.

Applications

[edit]Multiplexers are part of computer systems to select data from a specific source, be it a memory chip or a hardware peripheral. A computer uses multiplexers to control the data and address buses, allowing the processor to select data from multiple data sources

In digital communications, multiplexers allow several connections over a single channel, by connecting the multiplexer's single output to the demultiplexer's single input (Time-Division Multiplexing). The image to the right demonstrates this benefit. In this case, the cost of implementing separate channels for each data source is higher than the cost and inconvenience of providing the multiplexing/demultiplexing functions.

At the receiving end of the data link a complementary demultiplexer is usually required to break the single data stream back down into the original streams. In some cases, the far end system may have functionality greater than a simple demultiplexer; and while the demultiplexing still occurs technically, it may never be implemented discretely. This would be the case when, for instance, a multiplexer serves a number of IP network users; and then feeds directly into a router, which immediately reads the content of the entire link into its routing processor; and then does the demultiplexing in memory from where it will be converted directly into IP sections.

Often, a multiplexer and demultiplexer are combined into a single piece of equipment, which is simply referred to as a multiplexer. Both circuit elements are needed at both ends of a transmission link because most communications systems transmit in both directions.

In analog circuit design, a multiplexer is a special type of analog switch that connects one signal selected from several inputs to a single output.

Digital multiplexers

[edit]In digital circuit design, the selector wires are of digital value. In the case of a 2-to-1 multiplexer, a logic value of 0 would connect to the output while a logic value of 1 would connect to the output. In larger multiplexers, the number of selector pins is equal to where is the number of inputs.

For example, 9 to 16 inputs would require no fewer than 4 selector pins and 17 to 32 inputs would require no fewer than 5 selector pins. The binary value expressed on these selector pins determines the selected input pin.

A 2-to-1 multiplexer has a Boolean equation where and are the two inputs, is the selector input, and is the output:

- or

Which can be expressed as a truth table:

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 |

Or, in simpler notation:

| 0 | A |

| 1 | B |

These tables show that when then but when then . A straightforward realization of this 2-to-1 multiplexer would need 2 AND gates, an OR gate, and a NOT gate. While this is mathematically correct, a direct physical implementation would be prone to race conditions that require additional gates to suppress.[5]

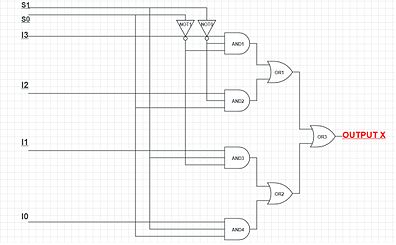

Larger multiplexers are also common and, as stated above, require selector pins for inputs. Other common sizes are 4-to-1, 8-to-1, and 16-to-1. Since digital logic uses binary values, powers of 2 are used (4, 8, 16) to maximally control a number of inputs for the given number of selector inputs.

-

4-to-1 mux

-

8-to-1 mux

-

16-to-1 mux

The Boolean equation for a 4-to-1 multiplexer is:

- or

Which can be expressed as a truth table:

| 0 | 0 | A |

| 0 | 1 | B |

| 1 | 0 | C |

| 1 | 1 | D |

The following 4-to-1 multiplexer is constructed from 3-state buffers and AND gates (the AND gates are acting as the decoder):

The subscripts on the inputs indicate the decimal value of the binary control inputs at which that input is let through.

Chaining multiplexers

[edit]Larger Multiplexers can be constructed by using smaller multiplexers by chaining them together. For example, an 8-to-1 multiplexer can be made with two 4-to-1 and one 2-to-1 multiplexers. The two 4-to-1 multiplexer outputs are fed into the 2-to-1 with the selector pins on the 4-to-1's put in parallel giving a total number of selector inputs to 3, which is equivalent to an 8-to-1.

List of ICs which provide multiplexing

[edit]

For 7400 series part numbers in the following table, "x" is the logic family.

| IC No. | Function | Output State |

|---|---|---|

| 74x157 | Quad 2:1 mux. | Output same as input given |

| 74x158 | Quad 2:1 mux. | Output is inverted input |

| 74x153 | Dual 4:1 mux. | Output same as input |

| 74x352 | Dual 4:1 mux. | Output is inverted input |

| 74x151A | 8:1 mux. | Both outputs available (i.e., complementary outputs) |

| 74x151 | 8:1 mux. | Output is inverted input |

| 74x150 | 16:1 mux. | Output is inverted input |

Digital demultiplexers

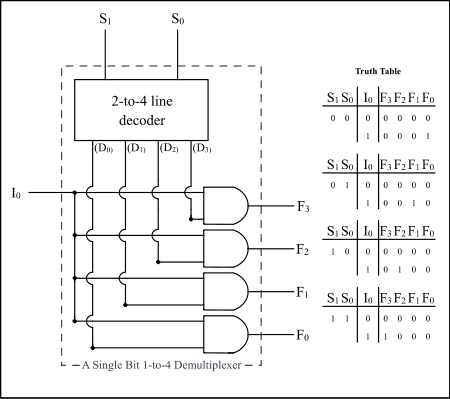

[edit]Demultiplexers take one data input and a number of selection inputs, and they have several outputs. They forward the data input to one of the outputs depending on the values of the selection inputs. Demultiplexers are sometimes convenient for designing general-purpose logic because if the demultiplexer's input is always true, the demultiplexer acts as a binary decoder. This means that any function of the selection bits can be constructed by logically OR-ing the correct set of outputs.

If X is the input and S is the selector, and A and B are the outputs:

List of ICs which provide demultiplexing

[edit]

For 7400 series part numbers in the following table, "x" is the logic family.

| IC No. (7400) | IC No. (4000) | Function | Output State |

|---|---|---|---|

| 74x139 | Dual 1:4 demux. | Output is inverted input | |

| 74x156 | Dual 1:4 demux. | Output is open collector | |

| 74x138 | 1:8 demux. | Output is inverted input | |

| 74x238 | 1:8 demux. | ||

| 74x154 | 1:16 demux. | Output is inverted input | |

| 74x159 | CD4514/15 | 1:16 demux. | Output is open collector and same as input |

Bi-directional multiplexers

[edit]Bi-directional multiplexers are built using analog switches or transmission gates controlled by the select pins. This allows the roles of input and output to be swapped so that a bi-directional multiplexer can function both as a demultiplexer and multiplexer.[6]

Multiplexers as PLDs

[edit]Multiplexers can also be used as programmable logic devices, to implement Boolean functions. Any Boolean function of n variables and one result can be implemented with a multiplexer with n selector inputs. The variables are connected to the selector inputs, and the function result, 0 or 1, for each possible combination of selector inputs is connected to the corresponding data input. If one of the variables (for example, D) is also available inverted, a multiplexer with n-1 selector inputs is sufficient; the data inputs are connected to 0, 1, D, or ~D, according to the desired output for each combination of the selector inputs.[7]

Unconventional use of multiplexers for arithmetic

[edit]Multiplexers have found application in unconventional stochastic computing (SC), particularly in facilitating arithmetic addition. In this paradigm, data is represented as a probability bitstream where the number of '1' bits signifies the magnitude of a value. Thus, the function of a 2-to-1 multiplexer can be conceptualized as a probability function denoted as:

, where a and b are the input bitstream and s is the select input. Using the select input = 0.5 yields:

While this approach doesn't yield exact addition but rather scaled addition, it is deemed acceptable in most SC studies. Multiplexers are extensively utilized for tasks such as average addition, average pooling, and median filtering within SC circuits. Moreover, more sophisticated applications of multiplexers include serving as Bernstein polynomial function generator,[8] capable of producing arbitrary mathematical functions within the SC domain. Recent research has also revealed that combinations of multiplexers can facilitate large-scale multiply-accumulate operation,[9] demonstrating feasibility in accelerating convolutional neural network on field-programmable gate arrays.

See also

[edit]- Digital subscriber line access multiplexer (DSLAM)

- Inverse multiplexer

- Multiplexing

- Priority encoder

- Rule 184, a cellular automaton in which each cell acts as a multiplexer for the values from the two adjacent cells

- Statistical multiplexer

- Ternary conditional operator

References

[edit]- ^ a b Dean, Tamara (2010). Network+ Guide to Networks. Delmar. pp. 82–85. ISBN 978-1423902454.

- ^ Debashis, De (2010). Basic Electronics. Dorling Kindersley. p. 557. ISBN 9788131710685.

- ^ Lipták, Béla (2002). Instrument engineers' handbook: Process software and digital networks. CRC Press. p. 343. ISBN 9781439863442.

- ^ Harris, David (2007). Digital Design and Computer Architecture. Penrose. p. 79. ISBN 9780080547060.

- ^ Crowe, John; Hayes-Gill, Barrie (1998). "The multiplexer hazard". Introduction to Digital Electronics. Elsevier. pp. 111–3. ISBN 9780080534992.

- ^ "Are switches & multiplexers bidirectional? | Video | TI.com". Texas Instruments. Retrieved 2023-08-03.

- ^ Lancaster, Donald E. (1974). The TTL Cookbook. H.W. Sams. pp. 140–3. ISBN 9780672210358.

- ^ Najafi, M. Hassan; Li, Peng; Lilja, David J.; Qian, Weikang; Bazargan, Kia; Riedel, Marc (2017-06-29). "A Reconfigurable Architecture with Sequential Logic-Based Stochastic Computing". ACM Journal on Emerging Technologies in Computing Systems. 13 (4): 57:1–57:28. doi:10.1145/3060537. ISSN 1550-4832.

- ^ Lee, Yang Yang; Halim, Zaini Abdul; Wahab, Mohd Nadhir Ab; Almohamad, Tarik Adnan (2024-03-04). "Stochastic Computing Convolutional Neural Network Architecture Reinvented for Highly Efficient Artificial Intelligence Workload on Field-Programmable Gate Array". Research. 7: 0307. Bibcode:2024Resea...7..307L. doi:10.34133/research.0307. ISSN 2639-5274. PMC 10911856. PMID 38439995.

Further reading

[edit]- Mano, M. Morris; Kime, Charles R. (2008). Logic and Computer Design Fundamentals (4th ed.). Prentice Hall. ISBN 978-0-13-198926-9..

External links

[edit] Media related to Multiplexers at Wikimedia Commons

Media related to Multiplexers at Wikimedia Commons The dictionary definition of multiplexer at Wiktionary

The dictionary definition of multiplexer at Wiktionary