Hitachi 6309

Hitachi 63C09E, a 3MHz external clock version of the 6309 | |

| General information | |

|---|---|

| Launched | 1982 |

| Common manufacturer | |

| Performance | |

| Max. CPU clock rate | 1 MHz to 5 MHz |

| Data width | 8-bit |

| Address width | 16-bit |

| Physical specifications | |

| Packages |

|

| History | |

| Predecessor | Motorola 6809 |

The 6309 is Hitachi's CMOS version of the Motorola 6809 microprocessor, released in late 1982. It was initially marketed as a low-power version of the 6809, without reference to its many internal improvements.

While in "Emulation Mode" it is fully compatible with the 6809. To the 6809 specifications, it adds higher clock rates, enhanced features, new instructions, and additional registers. Most of the new instructions were added to support the additional registers, as well as up to 32-bit math, hardware division, bit manipulations, and block transfers. The 6309 is generally 30% faster in native mode than the 6809.

This information was never published by Hitachi. The April 1988 issue of Oh! FM, a Japanese magazine for Fujitsu personal computer users, contained the first description of the 6309's additional capabilities. Later, Hirotsugu Kakugawa posted details of the 6309's new features and instructions to comp.sys.m6809.[1] This led to the development of NitrOS-9[2] for the Tandy Color Computer 3.

Programming model

[edit]

Differences from the Motorola 6809

[edit]The 6309 differs from the 6809 in several key areas.

Process technology

[edit]The 6309 is fabricated in CMOS technology, while the 6809 is an NMOS device. As a result, the 6309 requires less power to operate than the 6809.

The low-power use also means it can be paused for up to 15 cycles as it does not have to constantly refresh its internal state. This is useful for direct memory access as it allows external devices to pause the CPU to release the memory bus, read or write small amounts of memory, and then unpause the CPU again. No other logic is required.

It is a dynamic design. The datasheet specifies a minimum clocking frequency and it will lose its state when the clock speed is too low.

Clock speed

[edit]The 6309 has B (2 MHz) versions as the 6809 does. However, a "C" speed rating was produced with either a 3.0 or 3.5 MHz maximum clock rate, depending on which datasheet is referenced. (Several Japanese computers had 63C09 CPUs clocked at 3.58 MHz, the NTSC colorburst frequency, so the 3.5 rating seems most likely). Anecdotal and individual reports indicate that the 63C09 variant can be clocked at 5 MHz with no ill effects. Like the 6809, the Hitachi CPU comes in both internal and external clock versions (HD63B/C09 and HD63B/C09E respectively)

Computational efficiency

[edit]When switched into 6309 Native Mode (as opposed to the default 6809-compatible mode) many key instructions will complete in fewer clock cycles. This often improves execution speeds by up to 30%.

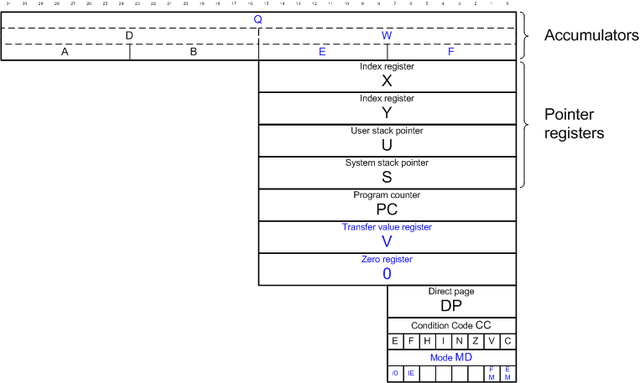

Additional registers

[edit]- Two 8-bit accumulators: 'E' and 'F'. These can be concatenated to form 16-bit accumulator 'W'. The existing 6809 16-bit accumulator D can be concatenated with W to form 32-bit accumulator 'Q'. It is likely that D is short for 'Double' and Q for 'Quad', the number of bytes they hold.

- Transfer register 'V' for inter-register instructions. Its value is unaffected by a hardware reset so it can retain a constant Value, hence 'V'.

- 8/16-bit Zero register '0' to speed up operations using a zero constant. This register always reads zero and writes to it are ignored.

- Mode register 'MD', a secondary Condition Code register that controls the operating mode. Only 4 bits of this register are defined.

Additional instructions

[edit]Most of the new instructions are modifications of existing instructions to handle the existence of the additional registers, such as load, store, add, and the like. Genuine 6309 additions include inter-register arithmetic, block transfers, hardware division, and bit-level manipulations. Further, 16 bit registers D and W can be target of 16 bit arithmetic with carry and 16 bit shift and rotate operations. On 6809, these operations are limited to 8 bit operands.

Despite the user-friendliness of the additional instructions, analysis by 6809 programming gurus[who?] indicates that many of the new instructions are actually slower than the equivalent 6809 code, especially in tight loops.[citation needed] Careful analysis should be done to ensure that the programmer uses the most efficient code for the particular application.

Most of new instructions use prefix opcode and that makes them slower by one cycle when compared to similar 6809 instruction. On other side, 6309 native mode executes many instructions faster by one or more cycles. Here is a timing comparison of an 8 bit LD instruction for 'A' register and 'E' register on 6809 and 6309:

| instruction | 6809 | 6309 emulation mode | 6309 native mode |

|---|---|---|---|

| LDA immediate | 2 cycles | 2 cycles | 2 cycles |

| LDE immediate | n/a | 3 cycles | 3 cycles |

| LDA direct | 4 cycles | 4 cycles | 3 cycles |

| LDE direct | n/a | 5 cycles | 4 cycles |

| LDA indexed | 4+ cycles | 4+ cycles | 4+ cycles |

| LDE indexed | n/a | 5+ cycles | 5+ cycles |

| LDA extended | 5 cycles | 5 cycles | 4 cycles |

| LDE extended | n/a | 6 cycles | 5 cycles |

Also inter-register operations and new 16 bit operations are somewhat mixed bag. Depending on addressing mode and 6309 mode, equivalent 6809 code can be faster. For illustration, let us look on timing of exclusive or instruction.

| instruction | 6809 | 6309 emulation mode | 6309 native mode |

|---|---|---|---|

| EORA immediate | 2 cycles | 2 cycles | 2 cycles |

| EORD immediate | n/a | 5 cycles | 4 cycles |

| EORA direct | 4 cycles | 4 cycles | 3 cycles |

| EORD direct | n/a | 7 cycles | 5 cycles |

| EORA indexed | 4+ cycles | 4+ cycles | 4+ cycles |

| EORD indexed | n/a | 7+ cycles | 6+ cycles |

| EORA extended | 5 cycles | 5 cycles | 4 cycles |

| EORD extended | n/a | 8 cycles | 6 cycles |

| EORR inter-register | n/a | 4 cycles | 4 cycles |

As table above indicates, exclusive or of 16 bit register D with immediate parameter can be replaced by two 8 bit instructions EORA imm, EORB imm and it will execute faster when 6309 runs in emulation mode. Though one should realize that sequence of 8 bit instructions EORA imm, EORB imm is not exact equivalent of 16 bit EORD imm instruction as condition code CC register is set according result of 8 bit operation in first case and according result of 16 bit operation in second case.

Similar issue is with inter-register EORR instruction. It accepts both 8 bit and 16 bit operands and it always executes within 4 cycles. However, for 8 bit operands, it is faster to use EORA imm or EORB imm instructions when appropriate. Further, when 6309 is running in native mode, instructions EORA direct, EORB direct take only 3 cycles, one cycle less than inter-register operation.

Additional hardware features

[edit]It is possible to change the mode of operation for the FIRQ interrupt. Instead of stacking the PC and CC registers (normal 6809 behavior) the FIRQ interrupt can be set to stack the entire register set, as the IRQ interrupt does. In addition, the 6309 has two possible trap modes, one for an illegal instruction fetch and one for division by zero. The illegal instruction fetch is not maskable, and many TRS-80 Color Computer users reported that their 6309's were "buggy" when in reality it was an indicator of enhanced and unknown features.

Undocumented Features

[edit]There is an additional register, called M, used for temporary storage that is available to use as well. [3]

References

[edit]- ^ "A Memo on the Secret Features of 6309". Google Groups comp.sys.m6809. Archived from the original on May 24, 2024. Retrieved September 17, 2024.

- ^ "The NitrOS-9 Project". SourceForge.

- ^ David Banks. "Undocumented 6309 Behaviours".

External links

[edit]- Article in the April 1988 issue of Oh! FM (Japanese)

- Hirotsugu Kakugawa's original "Secret 6309 features memo" and thread on Google's Usenet archive

- HD63B09EP Technical Reference Guide

- 6x09 Microprocessor Instruction Sets Archived 2016-10-23 at the Wayback Machine

- 6809/6309 Assembly and Mnemonic Information (PDF) By Chris Lomont, Version 1.2 May 2007]

- Comparison of 6809 and 6309 instruction list