File:Mips32 addi.svg

Appearance

Size of this PNG preview of this SVG file: 500 × 180 pixels. Other resolutions: 320 × 115 pixels | 640 × 230 pixels | 1,024 × 369 pixels | 1,280 × 461 pixels | 2,560 × 922 pixels.

Original file (SVG file, nominally 500 × 180 pixels, file size: 15 KB)

File history

Click on a date/time to view the file as it appeared at that time.

| Date/Time | Thumbnail | Dimensions | User | Comment | |

|---|---|---|---|---|---|

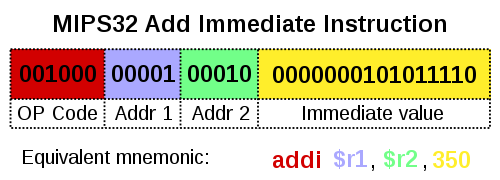

| current | 12:39, 12 November 2006 | 500 × 180 (15 KB) | German | {{Information |Description=This figure demonstrates how one type of MIPS32 instruction word is decoded. The first six bits specify the operation (add immediate). The second and third groups of five bits each specify the number of one of MIPS32's 32 genera |

File usage

The following 2 pages use this file:

Global file usage

The following other wikis use this file:

- Usage on ar.wikipedia.org

- Usage on ast.wikipedia.org

- Usage on bs.wikipedia.org

- Usage on ca.wikipedia.org

- Usage on de.wikipedia.org

- Usage on el.wikipedia.org

- Usage on en.wikibooks.org

- Usage on eo.wikipedia.org

- Usage on es.wikipedia.org

- Usage on es.wikibooks.org

- Usage on eu.wikipedia.org

- Usage on fa.wikipedia.org

- Usage on fr.wikipedia.org

- Usage on fr.wikibooks.org

- Usage on gu.wikipedia.org

- Usage on ha.wikipedia.org

- Usage on id.wikipedia.org

- Usage on ko.wikibooks.org

- Usage on mk.wikipedia.org

- Usage on om.wikipedia.org

- Usage on si.wikipedia.org

- Usage on tl.wikipedia.org

- Usage on zh.wikipedia.org